|

|

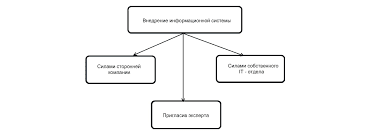

Одноразрядные двоичные сумматорыСтр 1 из 3Следующая ⇒ Реализация логических схем на компьютере с использование программы Electronics Workbench Правила сложения двоичных и десятичных чисел одинаковы: 1. сложение производиться поразрядно - от младшего разряда к старшему; 2. в младшем разряде вычисляется сумма младших разрядов слагаемых А; и Bj. Эта сумма в данной системе счисления может быть записана однозначным числом Si либо двухзначным числом PiS,. Функция Р называется переносом; 3. во всех последующих разрядах находиться сумма данных разрядов слагаемых А; и В„ причем при Ри-1 к этой сумме добавляется единица (в числовых примерах, приведенных выше, этот случай выделен жирным шрифтом, результат сложения в i-м разряде записывается в виде однозначного Si или двухзначного PjSi числа. Таким образом, в каждом разряде необходимо найти сумму A;, Bi и Рм (если Рм=1), т.е. определить Si и Pj. По числу входов различают полусумматоры, одноразрядные сумматоры (ОС) и многоразрядные сумматоры. Полусумматоры

Рис. 6.10 Схема полусумматора

Рис. 6.11 Схема полусумматора с использованием стандартной схемы сложения по модулю 2

Таблица 6.4 Таблица истинности полусумматора

Рис. 6.12 Диаграмма работы полусумматора Логические уравнения: S=xA*y+x*yA P=x*y 6.6.2 Одноразрядный двоичный сумматор

Рис. 6.13 Схема одноразрядного двоичного сумматора

Рис. 6.14 Диаграмма работы одноразрядного двоичного сумматора

Таблица 6.4 Таблица истинности сумматора

в Electronics Workbench.

Рис. 6.15 Схема последовательного сумматора

Рис. 6.16 Диаграмма работы последовательного сумматора Цифровые схемы сравнения

Цифровые схемы сравнения формируют на выходе F=l при равенстве подаваемых на вход двух двоичных чисел А (поразрядно записываем а и Ь) и В (с и d). Цифровая схема сравнения это цифровой аналог компаратора (см. рисунок 6.17), являющегося одним из важнейших устройств импульсной техники, временная диаграмма сумматоров приведена рисунке 6.18, приложения. На основе таблицы истинности для компаратора составим уравнения (для А>В, А<В, А^В), минимизируем их используя законы алгебры логики.

Рис. 6.18 Диаграмма работы цифровой схемы сравнения

Таблица 6.5 - Таблица истинности цифровой схемы сравнения Приложение 2 Микросхемы представляют собой четырехразрядный (двоичный) полный сумматор. Содержат 781 интегральный элемент. Корпус К155ИМЗ типа 238.16-2, масса не более 2 г., КМ155ИМЗ типа 201.16-6, масса не более 2,5 г.

238.16-1 238.16-2 Условное графическое обозначение вход слагаемого А4; выход суммы S3; 3 - вход слагаемого A3; 4 - вход слагаемого ВЗ; 5 - напряжение питания; 6 - выход суммы S2; 7 - вход слагаемого В2; 8 - вход слагаемого A3; 9 - выход суммы S1;

10 - вход слагаемого А1; 11 - вход слагаемого В1; 12 - общий; 13 - вход переноса РО; 14 - выход переноса четвкртого разряда Р4; 15 - выход суммы S4; 16 - вход слагаемого В4; Электрические параметры

Время задержки распространения по цепи переноса Зарубежные аналоги SN7483N, SN7483J Устройство. Работа выполняется на плате П6 с использованием одной технологической карты VI-1. Карта VI-1 позволяет исследовать АЛУ. При не нажатой кнопке SB2 общая шина подключается к выходу счетчика 10. Набирая любую необходимую информацию (кнопкой -SB1), контролируемую по индикатору HG-1 переписывают ее в регистры кода операций или операндов. Выход информации из АЛУ на индикатор HG-1 осуществляют сигналом, подаваемым на вход V микросхемы счетчика. Стандартное АЛУ типа К155ИПЗ, как известно [2], может выполнять 64 логических или арифметическо-логических операции, в зависимости от сигналов, подаваемых на управляющие входы S, М и вход переноса Р(). Для знакомства с принципом действия АЛУ можно ограничиться значительно меньшим набором операций. Список этих операций и соответствующие им коды приведены в таблице 2. Таблица входных кодов и выполняемых операций. Таблица 7.2 I

При работе со стендом карта (VI-1) удобнее пользоваться, шестнадцатеричным кодом операции, который набирается кнопкой, SB1 с контролем по индикатору HG1. Приложение 1 Приложение Микросхема представляет собой арифметико-логическое устройсво (АЛУ). Корпус К155ИПЗ типа 201.14-1, масса не более 1 г. Корпус ИМС К155ИПЗ

Условное графическое обозначение информационный вход младшего разряда ВО; информационный вход младшего разряда АО;

Одноразрядные двоичные сумматоры В цифровых устройствах применяются одноразрядные суммирующие схемы на два и три входа, причем первую называют полусумматором, вторую - полным одноразрядным сумматором. 6.3.1 Полусумматоры Простейшим суммирующим элементом является полусумматор. Он имеет (рис.6.3) два входа А и В для двух слагаемых и два выхода: Б(сумма) и РО (перенос). Обозначением полусумматора служат буквы HS (HalfSum - полусумма), работу прибора отражает таблица истинности таблица 6.1

Рис. 6.3 Полусумматор Полусумматор имеет два входа и пригоден для использования только в младших разряде. Рассмотрим синтез полусумматоров, имеющих два входа А и В. Выходными сигналами такого устройства являются сумма S и перенос РО, которые вырабатываются согласно таблице 1 функционирования данного устройства. Таблица 6.1

Рис. 6.4 Реализация полусумматора на элементах И-НЕ, И-ИЛИ-НЕ (а) и его условное обозначение (б) Сумматор в отличие от полусумматора должен воспринимать не два, а три входных сигнала: два слагаемых А, В и сигнал переноса с предыдущего разряда Р. Вообще говоря, сумматор можно построить из двух полусумматоров и одной схемы ИЛИ (рис. 6.5).

Рис.6.5 Полный одноразрядный сумматор на основе полусумматоров (а) и его условное обозначение (б)

Рассмотрим работу сумматора состоящего из двух полусумматоров, (рис 6.6)

Таблица 6.3

Рис. 6.7 Схема одноразрядного сумматора с парафазными входными сигналами 6.4 Параллельные многоразрядные сумматоры Параллельные многоразрядные сумматоры предназначены для одновременного суммирования двух многоразрядных чисел и характеризуются различными способами передачи сигналов переноса от младших разрядов сумматора к старшим. Различают параллельные комбинационные сумматоры с последовательным, одновременным и комбинированным переносом. Выбор типа переноса между разрядами суммирующего устройства определяется требованиями к быстродействию. Простейшими из параллельных сумматоров (ПС) являются ПС с последовательной передачей сигналов переноса (рис. 6.8). При последовательном вводе используется один, общий для всех разрядов полный сумматор с дополнительной цепью задержки. Оба слагаемых кодируются последовательностями импульсов, которые синхронно вводятся в сумматор через входы А и В, начиная с младших разрядов. Цепь задержки обеспечивает хранение импульса переноса Р на время одного такта, т.е. до прихода пары слагаемых следующего разряда, с которыми он будет просуммирован. Задержку обеспечивает D-триггер (триггер задержки). Для хранения и ввода слагаемых А и В, а так же для преобразования последовательного кода выходных импульсов в параллельный применяют регистры сдвига. Работа регистров и схемы задержки синхронизируется общим генератором тактовых импульсов. Сигнал переноса, образованный в младшем разряде, распространяется последовательно по цепям переноса к старшим разрядам. Время распространения переноса определяется суммарной задержкой этих цепей.

Ь2 Ьп Рис. 6.8 Комбинационный n-разрядный сумматор с последовательным переносом Быстродействие сумматора при сложении двух n-разрядных чисел характеризуется временем суммирования, которое в наихудшем случае равно ts=(n-l)tP+tiS где tis, tP - задержки формирования одноразрядным сумматором суммы и переноса соответственно. Следовательно, сумматоры с последовательным переносом обладают низким быстродействием. С целью повышения быстродействия (сокращения времени сложения) применяются сумматоры с одновременным переносом. Серьезным недостатком сумматоров с одновременным переносом является значительный рост аппаратурных затрат при построении схем межразрядных переносов. Поэтому на практике применяют метод построения сумматоров с комбинированным переносом. В сумматорах с комбинированным переносом полные одноразрядные сумматоры объединяются в группы. Внутри группы, как правило, осуществляется одновременный перенос. Между группами перенос может быть как последовательный, так и одновременный. На рис.6.9 в качестве примера приведена схема 16-разрядного двоичного сумматора с комбинированным переносом на базе четырехразрядных схем сумматоров АЛУ (микросхем ИГО). Здесь внутри групп организован одновременный перенос, между группами -последовательный.

Рис.6.9 16-разрядный сумматор с комбинированным переносом Для удобства построения сумматоров с одновременным переносом в ряде серий микросхем логические функции, формирующие переносы, реализуются в виде отдельной микросхемы. 6.5ЛАБОРАТОРНАЯ РАБОТА № 6 Цель работы: Исследовать четырехразрядный параллельный сумматор. Объем заданий к работе: 1. На примерах рассмотрения арифметических действий над двоичными числами обоснуйте утверждение, что наиболее часто встречающейся операцией над числами в вычислительных устройствах и в ЭВМ является операция сложения. 2. Ответить, чем отличаются операции параллельного и последовательного суммирования. 3. По таблице вариантов, возникающих при сложении двух одноразрядных чисел, составить и объяснить буревые выражения для описания одноразрядного сумматора. 4. Продумать и зарисовать в тетради рабочие схемы для изучения работы параллельного 4-х разрядного сумматора. Зарисовать условно-графическое обозначение изучаемого устройства. 5. Продумать формы отчетных таблиц. 1. Собрать схему стенда для исследования работы 4-х разрядного параллельного сумматора (карта Ш-3). 2. Провести исследование работы 4-х разрядного параллельного сумматора. В процессе исследования провести суммирование 4-5 пар 4-х разрядных двоичных чисел (операндов). Формирование и промежуточное хранение операндов выполнять соответственно с помощью регистра RG и тумблеров SA4...SA1. Суммирование производить с учетом сигнала переноса (SB3). Результаты суммирования проверить при переводе значений операндов в десятичный код. 3. Провести вычисление 3-4 пар 4-х разрядных операндов, используя перевод вычитаемого в дополнительный код. Результаты вычитания проверить при переводе значений операндов в десятичный код. 4. Результаты исследования представить соответствующими таблицами. 5. Просмотр состояний входов и выходов SM производить с помощью устройства цифровой индикации в режимах представления информации в двоичном и шестнадцатеричном кодах. При зачете: 1. Произвести сравнительную оценку используемых ИС для построения сумматоров. 2. Указать, возможно, ли создание на базе ИС К155ИМЗ сумматоров большой разрядности. Работа выполняется на плате ПЗ с использованием технологической карта Ш-3 Карта Ш-3 предназначена для исследования работы сумматора двух 4-х разрядных двоичных чисел на ИМС типа К155ИМЗ (D2). Для задания двух 4-х разрядных слагаемых используются тумблеры SA1 - SA4 (слагаемое А) и регистр D1 (слагаемое В). Ввод слагаемого В в регистр может осуществляться как в параллельном (с тумблеров SA1-SA4), так и в последовательном (с кнопки SB2) режимах. Сигнал начального переноса Р0 подается с кнопки.SB3 через инвертор D 2.3, имеющийся в основном блоке. Индикация входных операндов А и В осуществляется двоичным восьмиразрядным индикатором HL2 - HL9, Сигнал переноса в сстарший (пятый) разряд подается на индикатор HL1. Сумма в четырех первых разрядах дешифруется в блоке индикации и высвечивается в виде шестнадцатеричного числа на семисегментном индикаторе. Приложение 1 Технологическая карта (шаблон) Ш-3

Система охраняемых территорий в США Изучение особо охраняемых природных территорий(ООПТ) США представляет особый интерес по многим причинам...  Что делает отдел по эксплуатации и сопровождению ИС? Отвечает за сохранность данных (расписания копирования, копирование и пр.)...  Что будет с Землей, если ось ее сместится на 6666 км? Что будет с Землей? - задался я вопросом...  Что делать, если нет взаимности? А теперь спустимся с небес на землю. Приземлились? Продолжаем разговор... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|