|

|

SiGe - a Basic Material for Silicon Technology"SiGe BiCMOS technology is mature and here to stay", says David Harame, Distinguished Engineer, IBM. He has been circling the globe for the past few years demonstrating SiGe is ready to become a part of the CMOS universe. It is a robust, high performance, cost effective way to fulfill the demands of the roadmap, which is based on Moore's Law. SiGe Milestones The history of germanium is as long as the history of integrated circuits. In 1948, Bill Schockley, one of the inventors of the transistors, suggested Ge heterojunctions in his original patent. Just a few years later Kroemer tried to build a SiGe HBT. Shortly thereafter, IBM began its work in SiGe. Its first breakthrough was in 1987. The upside of the discovery was the cost structure and economies of scale are similar to silicon-wafer processing, but the downside was an increase in manufacturing complexity and it took almost another ten years to overcome that hurdle. In 1996, it qualified the world's first manufacturable SiGe HBT process. Since then its goal has been to show silicon with germanium can achieve the high-frequency performance of any III-V chip and more. IBM promotes both its processes, tooling, and SiGe know-how, including the Unaxis UHV-CVD epitaxy system. "It is the only UHV-CVD non-selective technique which enables the growth of device quality layers at low temperature to allow almost arbitrary composition", says Harame. The first commercial applications of SiGe were power amplifiers and RF analog applications in the nineties. Today it is showing up optical networking chips, measurement tools, wireless, high-speed local area networks, and global positioning chips. SiGe is compatible with CMOS processes and intellectual property, enabling more leverage of existing know-how. This compatibility with CMOS enables SiGe to really break the cost barriers. SiGe BiCMOS sales totaled $320million in 2001. Of that total, 80% was made by IBM and used Unaxis tooling. In addition, IBM holds 80% of the $600 million a year global market for early SiGe transistors. The SiGe market is projected to grow to $2.7 billion by 2006 according to the "2002 McClean Report", published by research firm IC Insights Today. Performance The fastest circuit in any technology is a SiGe HBT Ring Oscillator. It can even beat InP with 55% less power and 15% lower swing. There is no further reason to use III-V now that SiGe has matured. It is no longer true to say III-V has the fastest circuits - SiGe is easily as fast as III-V. A SiGe HBT also has the fastest dynamic frequency divider in any technology. SiGe frequency output continues to improve. Alternatively, frequency can be a trade-off for power gains. The potential for integration in SiGe is tremendous. Harame shows a reference design belonging to an anonymous IBM customer who is using the IBM 0.18 micron SiGe BiCMOS process for a wireless chip that includes 6,000 HBTs, 7 million CMOS transistors, a noise isolation technology and a host of capacitors. "It is our most complicated chip with an RF analog system-on-chip that operates at 2 GHz", asserts Harame. IBM has selected the Unaxis SiGe epitaxy because it is a mature technology which has been manufactured since 1996. Its UHV-CVD non-selective technique grows device quality layers. The defects are very low, with few failures. "In fact, it doesn't get any better!" exclaims Harame. Now IBM is making a "smart investment" in bandgap engineering as a result of using Unaxis process tools. IBM has selected the Unaxis SIRIUS® as the "tool of choice" because the equipment has been tested and is fully functional. CMOS roadmap in trouble There are a couple of ways to achieve the continuous improved processing power and cost advantages that Moore's Law demands. Scaling is one of them. Scaling means to continuously shrink the size of integrated circuits, increasing the number of transistors in a sliver of silicon while increasing the size of the wafers they are processed on. This has worked well in the past, but scaling is leading to an almost unmanageable level of complexity. Not only is complexity increasing but the industry is reaching its physical limits as oxide thicknesses shrink to only a few atomic layers of thickness. The leveling of scaling power also has to do with costs. The capital expenditures required to achieve these increments is becoming prohibitively expensive. A new fab has a price tag of $2 to 3 billion attached to it these days. An alternative to scaling to achieve performance gains and fulfill the demands of Moore's Law is to use advanced materials processes, such as compound semiconductors which boost performance because of their physical properties (e.g. SiGe's molecular structure enables electrons to pass across the circuits faster, plus the signals gain energy better than Si alone). Implicit to Moore's Law is that it features performance benefits, and innovations do not cost more than the market is willing to bear. An economy of scale must be in place. For the past 30 years, transistor scaling has been enabling the leap every eighteen months without significant changes in the CMOS manufacturing process as demanded by the industry roadmap. However, the economics of CMOS scaling are no longer valid. Gross margins are narrowing at the same time as capital expenditures required to build our next-generation fabs is climbing dramatically. Strained silicon provides a path. "I suggest that strained silicon CMOS is the answer to the limits described," says Harame. It has been shown that pulling silicon crystals apart or straining the silicon enables electrons to move throughout the circuits much faster. It improves electron flow by 70% and chip performance by 35%. A few issues remain to be overcome for the use of strained silicon - once wafer costs are addressed, the next consideration for this technology is the ease of fabrication of strained Si devices and circuits. Such chips are manufacturable today, however the straining process does introduce defects. There is still much to be understood about relaxation mechanisms and control dislocation densities and surface morphology. (Chip) High-Performance Bipolar Transistors With SiGe:C and Poly-SiGe

The successful use of poly-SiGe as the extrinsic base layer in a self-aligned process with non-selective epitaxy of SiGe:C for the intrinsic base.

The performance of silicon-based high-speed bipolar transistors has greatly improved over the last few years. Recently, a transistor with a record cut-off frequency of 210 GHz was presented by IBM [1]. The basis of this technology is an epitaxially grown SiGe base, making it possible to engineer the band gap and achieve a narrower base than ever before. The inevitable boron out-diffusion from the base layer can be minimized by the addition of carbon. Because of its relative simplicity non-selective epitaxy is commonly used for this type of device. One drawback is the subsequent non-self-aligned patterning of the layers necessary to build up the emitter and the connections to the base [1, 2]. So far, only a rather complicated process flow has been demonstrated, which includes conversion of poly-Si to oxide for the manufacture of self-aligned transistors from a non-selective epitaxially grown base [3]. Another approach starts with a selectively grown base layer in the emitter window [4]. However, selective epitaxy is known to suffer from severe loading effects. This means the epitaxial parameters will need to be tuned for each layout with a different device density. Moreover, the selective process is very difficult to control, which easily leads to voids and poor base contacts. A common problem in all self-aligned double-poly processes is related to the subsequent removal of the silicon used for the extrinsic base inside the emitter opening without etching down into the underlying monocrystalline silicon. This becomes more severe for a process involving an epitaxial base: since the base layer is formed prior to the emitter window etch as opposed to a process where the base formed by ion implantation through the etched emitter opening. Many solutions have been suggested in literature. In the case ot SiGe-based non-selective epitaxy, the etching problem has recently been addressed [5]. Here, a boron silicate glass (BSG) layer was used both as an etch stop and as a diffusion source for the electrical link-up between the external and the internal parts of the base. This article is based on a recently presented conference paper [6]. All SiGe-depositions have been performed in a Unaxis SIRIUS® UHV-CVD system. The modular concept used for the extrinsic base can also be applied to a more conventional double-poly bipolar process flow which uses an implanted base. Device manufacture The fabrication of the device follows an earlier process scheme up to the formation of the collector contact [7]. A nitride and silicon seed layer are then deposited and patterned prior to a non-selective SiGe:C epitaxy of the intrinsic base. This is followed by the deposition of a bi-layer of poly-SiGe and poly-Si for the extrinsic base layer. Before the deposition of an oxide, the extrinsic base region is implanted with a high dose of boron. The implanted boron will later be out-diffused, thereby forming the extrinsic base connection. The stack is then patterned and etched to form the emitter window. Subsequent processing follows a conventional double-poly bipolar process flow. (Chip) Seeking a Comprehensive Automated Wafer Inspection The growth rate in the number of 300mm fabs is expected to continue at a feverish pace in the coming years as more and more manufacturers realize the significant cost savings over 200mm wafer manufacturing. With so many 300mm fabs sprouting up around the world, new problems have arisen. Very few equipment suppliers made the decision to "bite the bullet" at the beginning of the 300mm race by investing in the development necessary to enter the market. They are only now starting to see a return on their money. In fact the 300mm fab race today would be even more intense if it were not for the high startup costs and the relative scarcity of good, solid 300mm process, test and inspection equipment. This challenge leads to another: 300mm fab automation requires a lot of floor space. When floor space costs are so astronomical for a 300mm fab, the use of multiple tools to accomplish related tasks is a luxury most fabs cannot afford. This is especially true of wafer inspection equipment. The growing trend toward flipchip packaging requires new inspection technology for the 300mm fab. For this process a complete inspection of the bump is required. This has required one tool to measure the bump height and one tool to measure the bump diameter, position and damage. When a manufacturer is producing devices that will be assembled in both the traditional wire bond package and the flipchip package, additional inspection systems would be required. This is a waste of precious budget dollars for floor space, facilitization, engineering support and spare parts stock. In short, it presents a larger Cost of Ownership. The higher costs of 300mm tools make maximized throughput an imperative. In the past, a test engineer was resigned to the fact that it was necessary to gather different but related inspection data on different tools, often from different vendors. This is not acceptable for 300mm wafer manufacturing. Throughput should not be sacrificed to run wafers through additional process steps. It is widely recognized that operator-based manual inspection is greatly inefficient for 300mm wafer inspection. No 300mm fab can afford to lose hours per lot inspecting on even a sampled basis. If a lot should require a 100% inspection of every wafer, the loss of time increases from hours to days. There is also a loss of yield from inaccurate and non-repeatable inspections that result from human variance from operator to operator, shift to shift. Clearly a reliable comprehensive automated alternative is needed. There is now available a single system that can meet all of these needs. The WAV 1000 from Semiconductor Technologies and Instruments, Inc. (STI) successfully combines 100% 2D & 3D bump, probe mark, active die and ink dot inspection, at high inspection rates, into a single tool. Unlike other systems, available today, these inspections are accomplished on a wafer lot in a single pass. STI's patented Genius™ Self Teach software makes recipe setup a simple process. The end result is an increase in good solid inspection data, an increase in wafer throughput, and a decrease in costly Engineering setup time. STI provides a comprehensive automated inspection solution to the 300mm manufacturing community with the WAV 1000. STI has the largest install base for 300mm for post-fab. (Semiconductor Technologies &Instruments) Intel Quality The Quest for Accelerated Continuous Improvement.

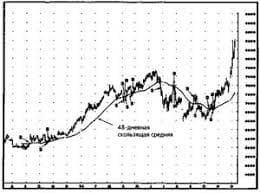

Over the last 20 years, product quality has taken on new meaning in the electronics industry. Customers have come to expect much higher levels of quality and reliability from their suppliers; as a result, the ability to manufacture defect-free products has become a necessity in the semiconductor arena. Companies can no longer compete in the global marketplace without demonstrating a firm commitment to reaching the ultimate goal of zero defects - and the perfection that level entails. Intel's efforts to improve quality over the past two decades and keep pace with customer demands have resulted in a dramatic reduction in product defects. Many of these changes are a direct result of the company's Accelerated Continuous Improvement (ACI) program, a systematic methodology that standardizes quality and reliability processes and tools across all Intel manufacturing operations. The ACI strategy consists of three principal goals: delivering consistently superior product quality, optimizing reliability through defect reduction, and understanding and meeting customer needs. In the never-ending race toward perfection, ACI ensures that Intel's customers receive the critical quality edge they need to compete successfully in today's increasingly volatile business climate. "Above all else, ACI is a process," said Intel executive vice president and chief operating officer Craig Barrett. With a Ph.D. in materials science and engineering from Stanford University, followed by a decade as a Stanford associate professor, Barrett knows this topic well. Perhaps more than anyone else, he has been responsible for driving Intel's quality improvement efforts since joining the company in 1974. "ACI is a set of standards that we adhere to rigorously across all of our operations. And when you consider the improvements we've made, the results speak for themselves."   ЧТО И КАК ПИСАЛИ О МОДЕ В ЖУРНАЛАХ НАЧАЛА XX ВЕКА Первый номер журнала «Аполлон» за 1909 г. начинался, по сути, с программного заявления редакции журнала...  Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот...  Система охраняемых территорий в США Изучение особо охраняемых природных территорий(ООПТ) США представляет особый интерес по многим причинам...  ЧТО ПРОИСХОДИТ ВО ВЗРОСЛОЙ ЖИЗНИ? Если вы все еще «неправильно» связаны с матерью, вы избегаете отделения и независимого взрослого существования... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|