|

|

Суперскалярные архите-ры проц-ов: проблемы и пути их решения.

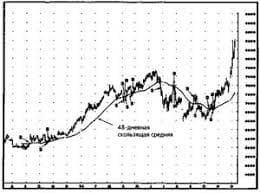

В суперскалярных процессорах реализована конвейерная обработка и параллельное выполнение команд. В обычном конвейере параллельное выполнение команд возможно только при нахождении команд на разных стадиях обработки (в разных сегментах конвейера). Суперскалярные процессоры позволяют выполнять несколько команд в одном сегменте конвейера. Несколько команд одновременно могут выполниться в течение одного такта. В суперскалярных процессорах используется несколько конвейеров, работающих параллельно, и устройства для интерпретации команд, снабженные логикой, позволяющие определить, являются ли команды независимыми. Параллельное выполнение команд не всегда возможно по причине тех же конфликтов, что и в конвейере. Для разрешения возможных конфликтов используют методы внеочередной выборки и завершения команд, прогнозирования переходов, условное выполнение команд и пр. Применяется динамическое распределение команд, причем порядок их выборки может не совпадать с порядком следования в программе (рис. 17). Естественно, результат выполнения должен совпадать с результатом строго последовательного выполнения. В суперскалярных компьютерах вопрос о параллелизме команд решается аппаратно. Программы для них совместимы на уровне бинарных (исполняемых) файлов. Недостатки: сложность аппаратной части; ограниченный размер окна выполнения, что уменьшает возможности определения потенциально параллельных команд. Представителями суперскалярных процессоров являются Pentium, PowerPC, K6/K7, Alpha.

суперскалярная организация процессора Пентиум достаточно проста для изучения, однако в ней отражены все особенности построения суперскалярных систем; система команд процессора Пентиум практически совпадает с системой команд широко известного семейства микропроцессоров i80x86, поэтому примеры программ легко воспринимаются; наконец, в процессоре Пентиум на программном и аппаратном уровне принято ряд решений, приближающих его архитектуру к архитектуре RISC-процессоров, позволяющих, однако, сохранить программную совместимость с большим объемом ранее написанного прикладного матобеспечения. Появление в структуре процессора более одного конвейера делает этот процессор суперскалярным. Как правило, в суперскалярных процессорах в первую очередь увеличивают количество целочисленных конвейеров, так как статистика показывает, что в обычных пакетах прикладных программ для ПЭВМ около 80% команд - целочисленные, 15% - команды условных переходов, и только небольшой процент команд является командами с плавающей запятой. Немедленно после введения второго или большего числа конвейеров возникают принципиально важные для суперскалярной структуры вопросы по организации и технической реализации вычислений:

Как организовать запуск параллельных команд во множественных конвейерах. Нетрудно видеть, что здесь решается и вопрос о распараллеливании последовательных программ. Как уменьшить отрицательное влияние на работу конвейеров зависимости по данным для смежных команд и потери быстродействия из-за появления в программе условных переходов. Планирование межконвейерного параллелизма должно производиться с учетом указанных эффектов. Как обеспечить повышенную пропускную способность всех видов памяти в суперскалярном процессоре, особенно если число одновременно выполняемых операций составляет 20-30. Каковы в перспективе предельные возможности, размеры суперскалярных процессоров. Организация параллельного запуска команд предусматривает выполнение трех этапов: распараллеливание последовательной программы; планирование порядка выполнения команд для заданных ресурсов; представление спланированной программы в фор-ме, пригодной для исполнения аппаратурой. В зависимости от способа реализации этих этапов методы формирования и запуска параллельных команд можно разделить на статические, динамические и смешанные. Считается, что статические способы предпочтительнее, поскольку анализ программы в процессе компиляции обеспечивает более глубокое выделение и планирование параллелизма, кроме того, исключает служебные команды управления параллелизмом из вычислительного процесса. Динамический же запуск позволяет более полно учитывать текущее состояние программы и ресурсов при исполнении программы. Возможны следующие способы статического формирования параллельной команды: Производится распараллеливание программы обычными методами, затем параллельные команды с помощью оптимизирующего планировщика упаковываются в виде СДК фиксированного формата. В таком СДК каждое поле формата закреплено за определенным конвейером и хранится в одной ячейке параллельной памяти. При чтении СДК из памяти выбираются все поля СДК независимо от их заполнения. Конвейеры запускаются синхронно в каждом такте. Это является возможным, поскольку в RISC-конвейерах основные операции выполняются за 1 такт. Основной недостаток схемы с фиксированным форматом СДК - неполное использование памяти при отсутствии команд в некоторых позициях СДК. Более полное использование ячейки памяти фиксированного формата применяется в МП i860 (рис. 4.8).

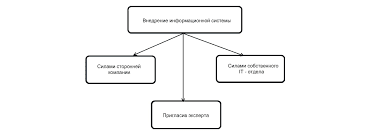

Система охраняемых территорий в США Изучение особо охраняемых природных территорий(ООПТ) США представляет особый интерес по многим причинам...  Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот...  ЧТО ТАКОЕ УВЕРЕННОЕ ПОВЕДЕНИЕ В МЕЖЛИЧНОСТНЫХ ОТНОШЕНИЯХ? Исторически существует три основных модели различий, существующих между...  Что делает отдел по эксплуатации и сопровождению ИС? Отвечает за сохранность данных (расписания копирования, копирование и пр.)... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|