|

|

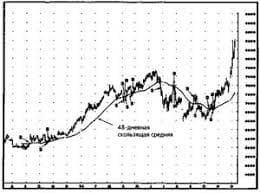

Память с синхронным интерфейсом — SDRAM и DDR SDRAMСтр 1 из 2Следующая ⇒ Для вычислительного конвейера, в котором могут параллельно выполняться несколько процессов и запросов к данным, гораздо удобнее синхронный интерфейс. В этом случае все события привязываются к фронтам общего сигнала синхронизации, и система четко “знает”, что, выставив запрос на данные в таком-то такте, она получит их через определенное число тактов. А между этими событиями на шину памяти можно выставить и другой запрос, и если он адресован к свободному банку памяти, начнется скрытая (latency) фаза его обработки. Таким образом удается повысить производительность подсистемы памяти и ее шины, причем не за счет безумного увеличения числа проводов (увеличения разрядности и числа независимых банков, о чем будет сказано позже). Микросхемы синхронной динамической памяти SDRAM (Synchronous DRAM) представляет собой конвейеризированные устройства, которые на основе вполне обычных ячеек (время доступа — 50–70 нс) обеспечивают цикл 5-1-1-1, но уже при частоте шины 100 МГц и выше. По составу сигналов интерфейс SDRAM близок к обычной динамической памяти: кроме входов синхронизации, здесь есть мультиплексированная шина адреса, линии RAS#, CAS#, WE (разрешение записи) и CS (выбор микросхемы) и, конечно же, линии данных. Все сигналы стробируются по положительному перепаду синхроимпульсов, комбинация управляющих сигналов в каждом такте кодирует определенную команду. С помощью этих команд организуется та же последовательность внутренних сигналов RAS# и CAS#, которая рассматривалась и для памяти FPM. Каждая микросхема внутренне может быть организована как набор из 4 банков с собственными независимыми линиями RAS#. Для начала любого цикла обращения к памяти требуется подать команду ACT, которая запускает внутренний формирователь RAS# для требуемой строки выбранного банка. Спустя некоторое количество тактов можно вводить команду чтения RD или записи WR, в которой передается номер столбца первого цикла пакета. По этой команде запускается внутренний формирователь CAS#. Передача данных для циклов записи и чтения различается. Данные для первой передачи пакета записи устанавливаются вместе с командой WR. В следующих тактах подаются данные для остальных передач пакета. Первые данные пакета чтения появляются на шине через определенное количество тактов после команды. Это число, называемое CAS# Latency (CL), определяется временем доступа TCAC и тактовой частотой. В последующих тактах будут выданы остальные данные пакета. После обращения необходимо деактивировать банк — перевести внутренний сигнал RAS# в пассивное состояние, то есть произвести предзаряд (precharge). Это может быть сделано либо явно командой PRE, либо автоматически (как модифицированный вариант команд RD или WR. Внутренние сигналы CAS# формируются автоматически по командам обращения и дополнительных забот не требуют. Регенерация выполняется по команде REF, за заданный период регенерации (стандартный 64 мс) должно быть выполнено 4096 или 8192 (в зависимости от объема микросхемы) команд REF. На первый взгляд из этого описания не видно никаких особых преимуществ SDRAM по сравнению с BEDO. Однако синхронный интерфейс в сочетании с внутренней мультибанковой организацией обеспечивает возможность повышения производительности памяти при множественных обращениях. Здесь имеется в виду способность современных процессоров формировать следующие запросы к памяти, не дожидаясь результатов выполнения предыдущих. В SDRAM после выбора строки (активации банка) ее можно закрывать не сразу, а после выполнения серии обращений к ее элементам, причем как по записи, так и по чтению. Эти обращения будут выполняться быстрее, поскольку для них не требуется подачи команды активации и выжидания TRCD. Максимальное время удержания строки открытой ограничивается периодом регенерации. Возможность работы с открытой строкой была использована уже в FPM DRAM. Однако в SDRAM можно активировать строки в нескольких банках — каждую своей командой ACT, эта особенность и стоит за словами “Single-pulsed RAS# interface” в перечислении ключевых особенностей SDRAM. Активировать строку можно во время выполнения любой операции с другим банком. Обращение к открытой строке требуемого банка выполняется по командам RD и WR, у которых в качестве параметров кроме адреса столбца фигурирует и номер банка. Таким образом можно так спланировать транзакции, что шина данных в каждом такте будет нести очередную порцию данных, и такой поток будет продолжаться не только в пределах одного пакета, но и для серии обращений к разным областям памяти. Кстати, держать открытыми можно и строки в банках разных микросхем, объединенных общей шиной памяти.

Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот...  Что делать, если нет взаимности? А теперь спустимся с небес на землю. Приземлились? Продолжаем разговор...  Живите по правилу: МАЛО ЛИ ЧТО НА СВЕТЕ СУЩЕСТВУЕТ? Я неслучайно подчеркиваю, что место в голове ограничено, а информации вокруг много, и что ваше право...  ЧТО ПРОИСХОДИТ, КОГДА МЫ ССОРИМСЯ Не понимая различий, существующих между мужчинами и женщинами, очень легко довести дело до ссоры... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|