|

|

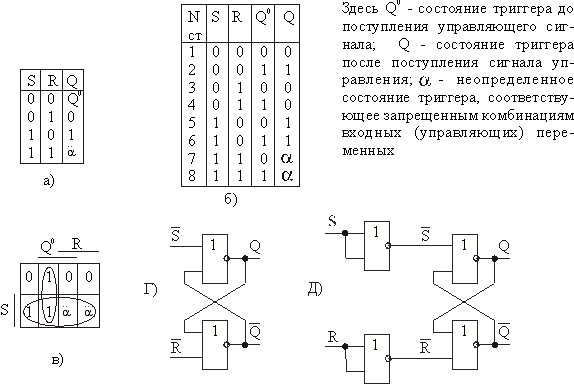

Триггеры как элементы памяти ЭВМ: основные типы и их реализация на основе логических элементов.Триггер - цифровой автомат, имеющий два устойчивых состояния равновесия либо 0, либо 1. Состояние триггера распознается по его входному сигналу. Под влиянием входного сигнала триггер скачкообразно переходит из одного устойчивого состояния в другое, при этом скачкообразно изменяется уровень напряжения его выходного сигнала. Для удобства использования в схемах вычислительных устройств триггеры обычно имеют два выхода: прямой Q (называется также “выход 1”) и инверсный Если хотя бы с одного входа информации в триггер заносится принудительно под воздействием синхронизирующего сигнала, то триггер называется синхронизируемым (синхронным). Если занесение информации в триггер с любого входа производится без синхронизирующего сигнала, то триггер называется несинхронизируемым (асинхронным). Состояние триггера определяется сигналом Q на прямом выходе триггера (или сигналом Законы функционирования триггеров задаются таблицами переходов с компактной записью, при которой в столбце состояний может быть указано, что новое состояние совпадает с предыдущим, либо является его отрицанием. Типы триггеров. Триггер типа RS имеет два входа раздельной установки в нулевое и единичное состояния. Воздействие по входу S (обозначен по первой букве слова set – установка) приводит триггер в единичное состояние, а воздействие по входу R (от первой буквы слова reset – сброс) – в нулевое. Одновременная подача сигналов S и R не допускается, что является недостатком для RS-триггера. RS – триггер показан на рисунке 1.

Рис. 1 Один из входов триггера называется установочным входом и обозначается буквой S, а другой – входом сброса и обозначается буквой R. Триггер имеет два симметричных выхода: прямой Схема RS-триггера, реализованного на элементах ИЛИ-НЕ и управляемая уровнем логической 1, приведена на рисунке 2,а, а схема RS-триггера, реализованного в базисах И-НЕ и управляемая низким уровнем, приведена на рисунке 2,б. Асинхронные RS-триггеры при наличии помех часто работают ненадежно. Например, короткие импульсы помехи, попадающие на R- и S-входы, могут изменить состояние триггера. Для повышения помехоустойчивости и устранения «состязаний» используют синхронный RS-триггер, УГО которого на принципиальных и функциональных схемах и его реализация на базе RS-триггера приведены на рисунках 3,а и 3,б.

а б Рис.2

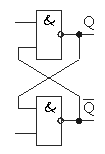

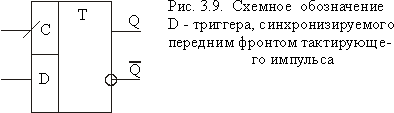

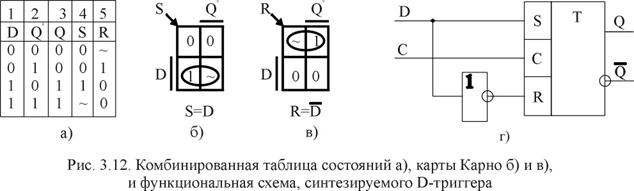

в а Рис. 3 Синхронный RS-триггер изменяет свое состояние только в те моменты времени, когда на специальный синхровход триггера С поступает разрешающий тактирующий импульс. Следует отметить, что для надежной работы триггера необходимо, чтобы длительность синхронизирующего сигнала не меньше времени переключения триггера. Рассмотренные выше RS-триггеры нельзя использовать в цифровых устройствах с обратными связями, так как изменения на входах и выходах происходят практически одновременно, что может привести к неопределенностям. Одним из самых широко используемых триггеров является D-триггер, который называют информационным триггером, а также триггером задержки. D-триггер бывает только синхронным. Он может управляться как уровнем тактирующего импульса, так и его фронтом. По синхроимпульсу D-триггер принимает то состояние, которое имеет входная линия D. УГО D-триггера приведено на рисунке 4а. На рисунке 4,б приведена функциональная схема D-триггера на основе синхронного двухступенчатого RS-триггера.

а б Рис.4 Обозначение JK-триггера на функциональных схемах приведено на рисунке 5,б. Выпускаемые промышленностью ИМС JK-триггеры могут иметь несколько входов (до трех) J и такое же количество входов K, объединенных схемами конъюнкций (рисунок 5,в).

в) Рис. 5 Т-триггер – это счетный триггер. Он имеет один вход, куда подают тактирующие (счетные) импульсы. Каждый синхроимпульс меняет состояние Т-триггера на обратное (аналогично состоянию JK-триггера при комбинации входных переменных J=1 и K=1). Частота следования импульсов на выходе счетного триггера в два раза меньше частоты входных синхроимпульсов, что позволяет их использовать в качестве делителей частоты. Для реализации делителя частоты на четыре потребуется два триггера, соединенных последовательно и т.д. Т-триггеры строятся только на базе двухступенчатых (RS, D, JK) триггеров. На рисунках 6,а и 6,б приведены схемы Т-триггера построенные на основе JK-триггера и D-триггера. Переключение состояния счетного триггера происходит в моменты поступления передних фронтов синхроимпульсов.

а б Рис.6

Вопрос №34   Конфликты в семейной жизни. Как это изменить? Редкий брак и взаимоотношения существуют без конфликтов и напряженности. Через это проходят все...  Система охраняемых территорий в США Изучение особо охраняемых природных территорий(ООПТ) США представляет особый интерес по многим причинам...  ЧТО И КАК ПИСАЛИ О МОДЕ В ЖУРНАЛАХ НАЧАЛА XX ВЕКА Первый номер журнала «Аполлон» за 1909 г. начинался, по сути, с программного заявления редакции журнала...  Живите по правилу: МАЛО ЛИ ЧТО НА СВЕТЕ СУЩЕСТВУЕТ? Я неслучайно подчеркиваю, что место в голове ограничено, а информации вокруг много, и что ваше право... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|