|

|

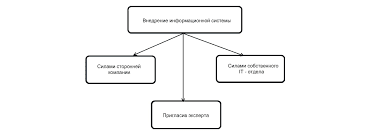

Процедура проектирования в Quartus IIСтр 1 из 14Следующая ⇒ Процедура проектирования устройств на ПЛИС включает в себя следующие этапы [1]. 1. Ввод проекта. На этом этапе разработчик вводит описание проекта и его частей. Проект или его части могут быть описаны традиционным способом в виде схемы, содержащей отдельные элементы, соединенные между собой цепями связи. Для создания и последующего редактирования таких описаний в пакете Quartus II используется графический редактор. Объектом его работы являются файлы с расширением .bdf. Графическое представление проекта в пакете Quartus II может создаваться, как в базисе библиотечных элементов, так и в базисе графических символов проектировщика. В качестве компонентов проекта Quartus II позволяет использовать IP (Intellectual Properties) ядра, представляющие собой единицы интеллектуальной собственности. Эти блоки являются полностью синтезируемыми, перемещаемыми и могут по желанию проектировщика располагаться в разных частях кристалла. Примерами IP ядер являются процессорные ядра NIOS II и большой набор различных контроллеров периферийных устройств. Главным достоинством графического способа ввода проекта является его традиционность и наглядность, связанная с привычностью разработчиков к восприятию изображений схем [1]. В настоящее время все большую популярность приобретают языки описания аппаратуры (HDL) [2,3]. Они допускают описание проектируемого устройства с точки зрения, как его поведения, так и структуры. Такие возможности позволяют представлять проект в форме текстового описания алгоритмов функционирования его модулей в сочетании с текстовым описанием межмодульных соединений для сложных проектов. Для создания и последующего редактирования текстовых описаний частей проекта в Quartus II используется текстовый редактор. Допустимыми являются языки VHDL, Verilog, AHDL (Altera HDL), System Verilog [5-7]. Соответствующие текстовые файлы имеют расширения .vhd, .v, .tdf, .sv. Достоинствами текстового описания проекта являются его компактность и относительная простота автоматизации любых преобразований, включая процесс создания описания, однозначность понимания и возможность переноса проектов в другие САПР. Quartus II допускает использование в проектах отдельных компонентов, созданных в системах автоматизации проектирования сторонних производителей. Такими компонентами могут быть и IP ядра. В этом случае, файл описания, как правило, представляет собой таблицу соединений конфигурируемых логических блоков и таблиц соответствия, выполненную до этапа размещения и разводки элементов. Соответствующие файлы имеют расширение .edf. 2. Компиляция проекта. Компиляция представляет собой процесс преобразования описания проекта в его структурную реализацию на выбранном кристалле ПЛИС. Компиляции может подвергаться как весь проект, так и отдельные его фрагменты. В Quartus II компиляция всегда выполняется для модуля верхнего уровня (top level). Поэтому для компиляции отдельного компонента схемы необходимо предварительно объявить его модулем верхнего уровня. Компиляция включает выполнение нескольких этапов. 2.1. Анализ и синтез. Составной частью процесса компиляции проекта является этап анализа и синтеза. Соответствующий модуль компилятора Quartus II строит базу данных проекта, которая объединяет все файлы описания проекта в единое целое с учетом иерархического представления проекта. Созданная база данных проекта в дальнейшем будет обновляться другими модулями компилятора до тех пор, пока не будет получен полностью оптимизированный проект. После своего создания база данных содержит только таблицу соединений проекта (netlist). После завершения полной компиляции – полностью оптимизированный, смонтированный проект, который используется для создания файлов, применяемых для временного моделирования, временного анализа, анализа потребляемой мощности и программирования кристалла. Модуль анализа и синтеза Quartus II выявляет синтаксические ошибки в проекте. Он проверяет логическую завершенность проекта, то есть возможность объединения файлов описания проекта в единое целое, и возможность реализации проекта на выбранном кристалле ПЛИС. Он также преобразует конструкции используемого языка HDL в их аппаратную реализацию на ресурсах кристалла таких, как функциональные преобразователи (lut), триггеры, защелки, логические элементы, блоки встроенной памяти, встроенные умножители. Рис. 1.3.1. демонстрирует реализацию этапа анализа и синтеза. Исходными файлами для выполнения этапа являются файлы с описанием модулей проекта на языках HDL (.vhd, .v, .tdf) и файлы со схемным представлением .bdf. На выходе получаются файлы отчета (.rpt, .htm) и созданная база данных (.rdb) [4].

Рис. 1.3.1. Этап анализа и синтеза проекта в Quartus II

Пакет Quartus II допускает использование средств синтеза сторонних производителей САПР. В этом случае, созданные проектировщиком файлы описания проекта на языке VHDL или Verilog, должны быть преобразованы средствами синтеза в файл соединений в формате EDIF (.edf) или файл Verilog Quartus Mapping File (.vqm), которые затем могут быть использованы в пакете Quartus II (см. рис. 1.3.1.). 3. Функциональное моделирование проекта. После завершения этапа синтеза проекта может быть выполнена верификация описания проекта. В основе верификации описания проекта лежит моделирование его работы при имитации различных внешних воздействий. Если при моделировании не учитываются задержки распространения сигналов, то такое моделирование называется функциональным. Существует два подхода к генерации внешних, относительно проекта, воздействий. Первый подход заключается в формировании воздействий путем задания последовательности входных сигналов в редакторе временных диаграмм. Второй подход состоит в написании специальной тестирующей программы с помощью одного из языков HDL. При использовании второго подхода тестируемый объект представляется как структурный компонент, соединенный с одной стороны с генератором тестовых воздействий, с другой стороны с анализатором реакций. Пакет Quartus II поддерживает реализацию обоих подходов. Верификация может быть выполнена как для отдельных частей проекта, так и для проекта в целом. Для выполнения этапа верификации также могут привлекаться средства моделирования, разработанные сторонними производителями САПР. 2.2. Размещение и трассировка. Модуль компилятора Quartus II, реализующий этот этап проектирования, называется Fitter. Он использует базу данных, созданную на предыдущем этапе модулем анализа и синтеза компилятора. Модуль Fitter осуществляет монтаж проекта в структуру выбранного кристалла программируемой логики. То есть, полученная на этапе синтеза модель полного представления проекта в техническом базисе кристалла отображается на внутренние ресурсы ПЛИС, которыми являются конфигурируемые логические блоки, блоки встроенной памяти, встроенные умножители и устанавливаются соответствующие соединения с помощью ресурсов трассировки кристалла. Модуль размещения и трассировки подбирает для каждой логической функции подходящее место на кристалле, с точки зрения уменьшения времени распространения сигнала, выполняет соответствующие соединения и назначения контактов ввода-вывода. Рис. 1.3.2. демонстрирует реализацию этапа размещения и трассировки. Исходными файлами для выполнения этапа являются файлы с расширением .cdb, созданные после выполнения синтеза компилятором и файлы с установками, имеющие расширение .qsf. На выходе получаются файлы отчета о компиляции (.rpt, .htm) и обновленная база данных [4].

При выполнении этапа размещения и трассировки пользователь может задать свои собственные назначения. Модуль размещения и трассировки реализует их, а затем выполняет оптимизацию оставшейся части проекта. После выполнения монтажа, пользователь может просмотреть результаты размещения и трассировки с помощью специального средства Chip Planner и, в случае необходимости, изменить некоторые назначения. Результатом компиляции проекта в пакете Quartus II является загрузочный файл, т.е. конфигурационная информация для выбранной микросхемы ПЛИС или для загрузочного ПЗУ этой интегральной схемы. Также создается файл отчета, содержащий информацию, как о процессе компиляции, так и о его результатах. В пакете Quartus II имеется специальное средство Resource PropertyEditor, называемое редактором топологии, с помощью которого можно вручную вмешаться в процесс компиляции и изменить структуру проекта на кристалле, например, с целью повышения производительности проектируемого устройства. 2.3. Временной анализ. Проверка соответствия реализованного проекта требованиям быстродействия. 2.4. Анализ потребляемой мощности. Проверка соответствия реализованного проекта требованиям по потребляемой мощности. 4. Временное моделирование на вентильном уровне. Осуществляется проверка правильности функционирования проекта после выполнения этапов синтеза, размещения и трассировки. 5. Программирование ПЛИС. Выполняется загрузка конфигурационной информации в программируемый кристалл, посредством чего реализуется пользовательский проект. 6. Тестирование и отладка проекта в составе системы. Проводятся комплексные испытания реализованного проекта, в результате чего принимается решение о соответствии проекта техническому заданию и завершении проектирования. В противном случае принимается решение о доработке проекта.   Система охраняемых территорий в США Изучение особо охраняемых природных территорий(ООПТ) США представляет особый интерес по многим причинам...  Что делает отдел по эксплуатации и сопровождению ИС? Отвечает за сохранность данных (расписания копирования, копирование и пр.)...  Конфликты в семейной жизни. Как это изменить? Редкий брак и взаимоотношения существуют без конфликтов и напряженности. Через это проходят все...  Что будет с Землей, если ось ее сместится на 6666 км? Что будет с Землей? - задался я вопросом... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|