|

|

СХЕМОТЕХНІКА МАЖОРИТАРНОЇ НАНОЕЛЕКТРОНІКИСигнал на виході мажоритарного елемента (МЕ) приймає значення, яке співпадає зі значеннями сигналів на більшості непарної кількості входів (мажоритарний принцип голосування). МЕ (рис.5.1) у порівнянні з базовими логічними елементами І, АБО, НІ дозволяють скорочувати та уніфікувати обладнання, мають більшу завадостійкість і надійність.

Рис.5.1. Мажоританий елемент 5.1. Інтегральний мажоритарний елемент МЕ працює за принципом вибору більшості, тому його вихідний сигнал f дорівнює:

де Наприклад, одна з можливих ТТЛ-мікросхем, що реалізує МЕ вибору (2 з 3), наведена на рис.5.2. Якщо

а)

б)

в) Рис.5.2. Умовне позначення (а), спрощена електрична схема (б) та таблиця дійсності (в) мажоритарного елемента (2 з 3) Мала частина струму відокремлюється в практично закритий діод VD, та через емітерний перехід транзистора VT2:

Для зменшення цього струму та пришвидшення вимикання транзистора VT2 ставлять інколи додаткове джерело – Езв. Струм бази третього транзистора VT3

має достатнє значення для насичення і відкривання VT3, тому У цій таблиці у кожній (!) строці дужками позначені сигнали, які можуть приймати протилежне значення в результаті дії завад, при цьому вихідні функції не змінюються. На першому та останньому наборах завади на будь – якому з входів не викликають спотворень вихідного сигналу. З таблиці слідує, що мажоритарна функція трьох аргументів дорівнює кількості співіснувань з 3 по 2:

(5.6) Елемент на рис.5.1, а зветься універсальним МЕ (УМЕ). Для тотожних перетворень мажоритарних функцій використовують деякі рівносильності:

5.2. Нанохеми на одноелектронних мажоритарних елементах Функцію мажоритарного вибору (5.5) можливо реалізувати на базі трьох одноелектронних логічних елементів DD1, DD2 та DD3(рис.3.10, а) і одного 3АБО DD4, який подібний схемі 2АБО (рис.3.11, а). На рис.5.3 приведена саме така реалізація МЕ (2 з 3).

Рис. 5.3. Синтез МЕ 2 з 3 (а), умовне позначення (б) та одноелектронна наносхема Інший спосіб створення МЕ на одноелектронних транзисторах показан на рис. 5.4.

Рис.5.4. Схема МЕ (2 з 3) Ця схема зібрана на двох логічних елементах 2І DD1 та DD3 (рис.3.10,а), двох елементах 2АБО DD2 та DD4 (рис.3.11, а) та одному інверторі DD5 (рис.3.5, а). На базі трьох одноелектронних універсальних МЕ (рис.5.3, в) реалізують однорозрядний суматор (рис.5.5, а).

Рис.5.5. Однорозрядний суматор на універсальних МЕ (а) та його умовне позначення (б) Логічні рівняння цього суматора:

або мажоритарні рівнозначності:

5.3. Нанохеми на комплементарних одноелектронних мажоритарних елементах Універсальний мажоритарний елемент (2 з 3) реалізован (рис.5.6) на двох логічних інверторах DD1 та DD2, елементною базою яких є дві пари комплементарних ОЕТ.

Рис.5.6. УМЕ 2 з 3 на базі КОЕТ-інверторів (а) та його умовне позначення (б) Для виконання функції мажоритарного вибору три входи УМЕ х1, х2 та х3 з’єднані через шість спеціально налаштованих конденсаторів С1-С6 з двома кулонівськими острівцями КО1 і КО2. Ці нанорозмірні конденсатори подібні шістьом емітерним переходам транзистора інтегральної мікросхеми МЕ, приведеної на рис.5.2, б. Ємності мають бути рівними: С1=С2=С3=С4=С5=С6= Якщо два чи три вхідних сигнали дорівнюють 1: х1х2х3 ={011, 101, 110, 111}, то сумарний вхідний сигнал При конструюванні КОЕТ-двоінвертної схеми універсального МЕ дуже важливо запобігати міжвходовим перехресним завадам. Тому слід точно дотримуватись умов рівняння (5.9). Інші ємності цієї схеми мають значення: Cв1 = Св3 = Сс2 = Сс4 =1аФ, Св2= Св4 = Сс1= Сс3 =2аФ, С7 =С8 = С12 = С13=9аФ, С9 = С14 =24аФ, а Ес =+6,5мВ. На рис.5.7 побудована характеристика перемикання УМЕ при цьому наборі параметрів та при Т=10мК, коли на всіх входах х1 =х2 =х3 =1.

Рис.5.7. Характеристика перемикання УМЕ на двох КОЕТ-інверторах На характеристиці (рис.5.7) у вузькій зоні перемикання Uвх На базі УМЕ з комплементарними інверторами (рис.5.6) створено однорозрядний наносуматор, схема якого наведена на рис.5.8.

Рис.5.8. Схема однорозрядного наносуматора на УМЕ (а) та його умовне позначення (б) На рис.5.9 показані результати моделювання осцилограм функціонування однорозрядного суматора при Т=2мК. Процеси тунелювання електронів скрізь переходи КОЕТ носять балістичний характер, тому ці часові характеристики є середньостатичними по невеликій кількості електронів, які накопичуються на кулонівських острівцях після тунелювання.

Рис.5.9. Часові діаграми виконання операції додавання суматором на УМЕ і таблиця дійсності З порівняння рис.5.9 та рис.4.5 видно, що швидкодія суматора на УМЕ на порядок вища, ніж у суматора на КОЕТ. У багаторозрядних суматорів паралельної дії додавання виконується одночасно по усім розрядам бінарних чисел. Такий суматор повинен мати окремі вузли додавання у кожному розряді. Для прикладу на рис. 5.10 приведена структура 4-розрядного суматора, яка виконана з використанням чотирьох однорозрядних DD0-DD3 на базі УМЕ (рис. 5.8). Вочевидь, реальний час виконання операції додавання (х3х2х1х0+у3у2у1у0) визначається часом переносу сигналу С до наступного розряду.

Рис.5.10. Структурна схема паралельного 4-розрядного суматора на універсальних МЕ На рис. 5.11 побудовані модельні діаграми роботи 4-розрядного суматора та таблиця станів додавання чисел х3х2х1х0 = 1111 та у3у2у1у0 = 0001.

а) б) Рис.5.11. Часові діаграми (а) та таблиця станів 4-розрядного суматора (б) для додавання чисел х3х2х1х0 = 1111 та у3у2у1у0 = 0001 Середній час виконання операції додавання з переносом до старшого розряду складає орієнтовно 1,5 нс.

5.4. Нанохеми на мажоритарних елементах з нереверсивними тунельними переходами Коли об’єднати два тунельних переходи, які мають порогові характеристики кулонівської блокади, з трьома входами, то отримують МЕ з нереверсивними тунельними переходами (МЕТП). На рис.5.12 показана схема послідовного з’єднання двох тунельних переходів Сп1 і Сп2, конденсатора навантаження

Рис.5.12. Нереверсивний наноприлад на одноелектронних тунельних переходах При низьких температурах

Кількість накопичених електронів

Рис.5.13. Характеристики накопичення-втрат електронів на кулонівському острівці KO2 для нереверсивних тунельних переходів Кількість тунелюючих електронів

В протилежний бік, зменшення n від одного до нуля відбувається за рахунок переходу електрона до джерела

де Наприклад, при Залежність вузлової напруги на острівці

МЕТП (2 із 3) конструюють на базі нереверсивного одноелектронного приладу з додаванням трьох входів (рис. 5.14, а).

Рис. 5.14. Схема МЕТП (а) та його умовне позначення (б) Цей прилад складений з двох симетричних тунельних переходів з параметрами два рівня напруги, що визначаються пороговими функціями (5.11) і (5.12). Принцип дії МЕТП (2 з 3) полягає в наступному. Якщо на двох чи трьох входах схеми діють позитивні рівні логічної одиниці

підвищують позитивний потенціал

Вочевидь, при цих часових та амплітудних співвідношеннях

Коли ж на вході МЕТП діють два чи три сигнали логічного нуля, то тунелювання відсутнє, а на виході схеми під дією напруги зберігання

Отже, виконуються умови мажоритарного вибору (2 з 3) із запереченням. На рис. 5.15 побудований ряд статичних перехідних характеристик МЕПТ (2 з 3) при чотирьох різних наборах вхідних параметрів

Рис.5.15. Результати моделювання прохідних характеристик МЕПТ (2 з 3) при різних наборах трьох вхідних сигналів Переривистою лінією в центрі побудоване геометричне місце точок перемикання схеми, якщо всі входи заземлені (занулені) Збільшуючи кількість позитивних рівнів вхідних сигналів логічної одиниці від двох (+4мВ,+4мВ,-4мВ) до трьох (+4мВ,+4мВ,+4мВ), зменшують напругу перемикання до +56мВ і до +48мВ. В протилежний бік, якщо збільшувати кількість негативних сигналів логічного нуля від двох (+4мВ,-4мВ, -4мВ) до трьох, то напруга перемикання зростає до 64мВ і до 72мВ. Вихідні логічні рівні при цьому залишаються без змін: -4мВ та +4мВ Рис. 5.16 ілюструє імпульсний режим динамічної роботи схеми МЕТП (2 з 3) при

Рис.5.16. Осцилограми функціювання мажоритарного наноелемента з нереверсивними переходами Отже, завдяки гістерезисним характеристикам перемикання (рис.5.15) та дворівневому імпульсному керуванню, схема МЕТП (рис.5.14) виконує функцію мажоритарного вибору (2 з 3). При конструюванні логічних схем на МЕТП реалізують каскадне з’єднання, при якому, по-перше, вихідний конденсатор попереднього елементу є вхідним для наступного (рис.5.17, а), а по-друге, використовують трифазне, з перекриттям імпульсів, керування (рис.5.17, б).

Рис.5.17. З’єднання логічних схем на МЕТП(а) та часові діаграми трифазного керування (б) Ця схема реалізує заперечення мажоритарного вибору (4 з 7):

Таким чином, під’єднання до фазного керування здійснюється через два каскади, що забезпечує односторонню (нереверсивну) передачу інформації, як, наприклад, у приладів з зарядовим зв’язком (ПЗЗ). Подача імпульсів керування з перекриттям У якості прикладу виконання логічної операції додавання однорозрядних чисел з переносом є наносуматор, у якому використовують три групи МЕТП з трифазним керуванням (рис.5.18).

Рис.5.18. Схема однорозрядного наносуматора на МЕТП(а) та його умовне позначення (б) Наносуматор на МЕТП має по два прямих

і переносу до старшого розряду.

Логічне ядро наносуматора складають мажоритарні елементи DD2 та DD3, які виконують логічні функції додавання (5.20). Інші схеми (DD1, DD4 та DD5) узгоджують передачу сигналів мажоритарного вибору з синхроімпульсами фазового керування. Каскад з двох схем DD3 та DD6 реалізує тільки функцію переносу (5.21). Причому схема DD6 підвищує навантажувальну здатність наносуматора в цілому і працює під час дії напруги збудження на фазі Ф3, тобто, синхронно з вихідним МЕТП DD7. Зазвичай, затримка між вхідним сигналом Таким чином, у нереверсивних мажоритарних елементів логічні сигнали мають протилежні знаки потенціалів, і тому їх головна перевага перед іншими МЕ – це практично повна відсутність рівнів постійної напруги між каскадами. Головний же недолік – це складні схеми керування. Контрольні завдання до глави 5 5.1. Довести високу завадостійкість мажоритарного елемента (2 з 3) за його таблицею дійсності (рис.5.1, в). 5.2. Перевірити справедливість рівняння (5.6) для інверсного виходу універсального МЕ та співставити результати з таблицею дійсності на рис.5.1, в. 5.3. Скласти таблицю станів для виходів усіх логічних елементів в моделі МЕ на рис.5.3, в. 5.4. Скласти таблицю станів для виходів усіх логічних елементів в моделі МЕ на рис.5.4. 5.5. Для однорозрядного наносуматора на МЕ (рис.5.5, а) скласти таблицю дійсності. 5.6. Які функції буде виконувати універсальний МЕ, якщо в ньому об’єднати два входи в один, а на третьому підтримувати «0» або «1»? 5.7. На базі одного універсального МЕ (рис.5.3, б, в) реалізувати операцію 5.8. На базі одного універсального МЕ (рис.5.3, б, в) реалізувати операцію 5.9. На базі одного універсального МЕ (рис.5.3, б, в) реалізувати операцію 5.10. На базі одного універсального МЕ (рис.5.3, б, в) реалізувати операцію 5.11. На базі одного універсального МЕ (рис.5.3, б, в) реалізувати операцію 5.12. На базі одного п’ятивходового універсального МЕ реалізувати операцію 5.13. На базі одного п’ятивходового універсального МЕ реалізувати операцію 5.14. На базі одного п’ятивходового універсального МЕ реалізувати операцію 5.15. На базі одного п’ятивходового універсального МЕ реалізувати операцію 5.16. Яку кількість мажоритарних функцій можна реалізувати на МЕ з (2n-1) входами? 5.17. Для 4-розрядного наносуматора на МЕ (рис.5.10) побудувати таблицю станів для виконання операції додавання двох десяткових чисел (a+b), перевівши їх у бінарний код: [(x3x2x1x0) + (y3y2y1y0)]. Варіант визначається за списком або номером залікової книжки.

5.18. Реалізувати функцію додавання однорозрядного наносуматора 5.19. Побудувати повну таблицю дійсності для зовнішніх та внутрішніх з’єднань для наносуматора на УМЕ (рис.5.8, а). 5.20. Розрахувати порогові напруги U2 (5.13) та U1 (5.14) для мажоритарного наноелемента з шістьома тунельними переходами, якщо CН = 2аФ, а СП = 20 аФ. 5.21. Побудувати таблицю станів для МЕТП (рис.5.14, а та рис.5.16). 5.22. Розрахувати напруги збудження (5.15), збереження (5.16), U0вих (5.17) та U1вих (5.18), якщо ємність тунельних переходів СП МЕТП збільшилась у 2 рази. 5.23. Побудувати таблицю станів для каскадної системи з’єднання МЕТП (рис.5.17). 5.24. Побудувати таблицю станів для суматора на МЕТП (рис.5.18, а). 5.25. Яким має бути співвідношення логічних 0/1 для одноелектронного МЕ з (2n-1) входами, щоб на виході елемента отримати логічний 0? 5.26. Яким має бути співвідношення логічних 0/1 для одноелектронного МЕ з (2n-1) входами, щоб на виході елемента отримати логічну 1?

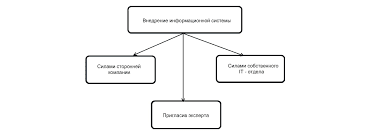

Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот...  Что делает отдел по эксплуатации и сопровождению ИС? Отвечает за сохранность данных (расписания копирования, копирование и пр.)...  ЧТО И КАК ПИСАЛИ О МОДЕ В ЖУРНАЛАХ НАЧАЛА XX ВЕКА Первый номер журнала «Аполлон» за 1909 г. начинался, по сути, с программного заявления редакции журнала...  Конфликты в семейной жизни. Как это изменить? Редкий брак и взаимоотношения существуют без конфликтов и напряженности. Через это проходят все... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|