|

|

Дополнительные интегральные микросхемы: контроллер прямого доступа, контроллер прерываний, математический сопроцессор.Интегра́льная (микро)схе́ма,чип, микрочи́п (англ. microchip, silicon chip, chip — тонкая пластинка — первоначально термин относился к пластинке кристалла микросхемы) — микроэлектронное устройство — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле (или плёнке) и помещённая в неразборный корпус, или без такового, в случае вхождения в состав микросборки. Часто под интегральной схемой (ИС) понимают собственно кристалл или плёнку с электронной схемой, а под микросхемой (МС) — ИС, заключённую в корпус. В то же время выражение «чип-компоненты» означает «компоненты для поверхностного монтажа», в отличие от компонентов для пайки в отверстия на плате. Поэтому правильнее говорить «чип-микросхема», имея в виду микросхему для поверхностного монтажа. На сегодняшний день большая часть микросхем изготавливается в корпусах для поверхностного монтажа. Контроллер прямого доступа к памяти (DMAC) Отличительные особенности: 1. Отвечает за высокоскоростную передачу данных · из памяти в УВВ · из памяти в память · из УВВ в память · из УВВ в УВВ 2. 4 канала 3. Передача за одну транзакцию от 1 байта до 16 Мбайт 4. Несколько режимов адресации для адреса источника и получателя · Инкрементный · Декрементный · Статический 5. Передача 1, 2, 4 или 8-байтных потоков 6. Программируемый приоритет между каналами Обзор Для передачи данных между встроенными запоминающими устройствами и УВВ в пространстве памяти данных у микроконтроллеров XMEGA A3 предусмотрен контроллер прямого доступа к памяти (DMA-контроллер). Для передачи данных DMA-контроллер и ЦПУ используют общую шину данных. Контроллер имеет 4 канала с возможностями раздельной конфигурации. Каждый канал DMA может передавать данные блоками конфигурируемого размера от 1 до 64 кбайт. При необходимости передачи за одну транзакцию до 16 Мбайт данных можно воспользоваться возможностью повторяющейся передачи. В настройках каждого из каналов DMA задается адрес источника и получателя данных, а также режим адресации: с инкрементируемым, декрементируемым или статическим адресом. Адресация источника и получателя данных независимая. По завершении текущей транзакции, исходный адрес источника и получателя может быть автоматически перезагружен для подготовки к следующей транзакции. DMA-контроллер имеет доступ ко всем УВВ через их расположенные в памяти ввода-вывода регистры. Кроме того, DMA можно использовать для автоматический передачи данных в коммуникационные модули и обратно, а также для автоматического считывания результата преобразования АЦП, передачи данных для преобразования в ЦАП, или изменения/опроса состояния линий ввода-вывода. Доступен для выбора широкий диапазон источников запуска передачи из УВВ, системы событий и программы. У каждого канала DMA имеются различные источники запуска передачи. Для непрерывной передачи данных можно чередовать работу двух каналов с тем, чтобы, по завершении передачи первым каналом, вступал в работу второй и наоборот. DMA-контроллер может считывать данные из EEPROM, но не может записывать в него данные и не имеет доступа к Flash-памяти. Контроллер прерываний Контроллер прерываний — микросхема или встроенный блок процессора, отвечающий за возможность последовательной обработки запросов на прерывание от разных устройств. Английское название — Programmable Interrupt Controller (PIC). Как правило представляет собой электронное устройство, иногда выполненное как часть самого процессора или же сложных микросхем его обрамления, входы которого присоединены электрически к соответствующим выходам различных устройств. Номер входа контроллера прерываний обозначается «IRQ». Следует отличать этот номер от приоритета прерывания, а также от номера входа в таблицу векторов прерываний (INT). Так, например, в IBM PC в реальном режиме работы (в этом режиме работает MS-DOS) процессора прерывание от стандартной клавиатуры использует IRQ 1 и INT 9. В первоначальной платформе IBM PC используется очень простая схема прерываний. Контроллер прерываний представляет из себя простой счётчик, который либо последовательно перебирает сигналы разных устройств, либо сбрасывается на начало при нахождении нового прерывания. В первом случае устройства имеют равный приоритет, во втором устройства с меньшим (или большим при обратном счёте) обладают большим приоритетом. В процессоре Pentium был добавлен расширенный контроллер прерываний (APIC). Он состоит из модуля, встроенного в сам процессор (в случае многоядерной системы — в каждое ядро), называемого локальный контроллер прерываний (local APIC), и центрального модуля, выполненного в одном экземпляре даже на многоядерном оборудовании, обычно как часть микросхем обрамления процессора (IO APIC). Проводники IRQ от устройств подсоединены к IO APIC. Для общения local APIС и IO APIC, а также local APIC различных ядер друг с другом, используется передняя (frontside) шина многопроцессорной системы, также используемая для соединения процессоров и контроллера памяти. Варианты использования передней шины для общения APIC между собой — отдельные проводники, или же специальные типы транзакций — менялись от поколения к поколению процессоров Pentium и Core. APIC использовался в многоядерных/многопроцессорных системах, начиная с Intel Pentium (ядро P54). Начиная с этого процессора, каждый следующий снабжался интегрированным Local APIC-ом. Преимущества расширенного контроллера прерываний: · возможность реализации межпроцессорных прерываний — сигналов от одного процессора другому поддержка до 256 входов IRQ, в отличие от 16 на классической IBM PC · крайне быстрый доступ к регистрам текущего приоритета прерывания и подтверждения прерывания. Контроллер прерываний, совместимый с IBM PC, исполнялся как устройство шины ISA с очень медленным доступам к его регистрам (порт 0x20). · APIC поддерживался в ОС Windows, начиная с Windows NT 4.0. В настоящий момент наблюдается тенденция к отказу от IO APIC, как и проводников IRQ, и переходу на Message Signaled Interrupts. Математический сопроцессор Математический сопроцессор - это специальный модуль для выполнения операций с плавающей запятой, который работает в содружестве с центральным процессором. Математический сопроцессор предназначен для расширения вычислительных возможностей центрального процессора — выполнения арифметических, тригонометрических, экспоненциальных и логарифмических операций. Сопроцессор поддерживает семь типов данных: 16-, 32-, 64-битные целые числа; 32-, 64-, 80-битные числа с плавающей точкой и 18-разрядные числа в двоично-десятичном формате. Формат чисел с плавающей точкой соответствует стандарту IEEE 754. Применение сопроцессора повышает производительность вычислений в сотни раз. С программной точки зрения сопроцессор и процессор выглядят как единое целое. Физически сопроцессор может быть отдельной микросхемой (387-й), подключаемой к локальной шине основного процессора, или располагаться прямо на кристалле центрального процессора (486+). В любом случае сопроцессор исполняет только свои специфические команды, а всю работу по декодированию инструкций и доставке данных осуществляет CPU. Сопроцессор может выполнять вычисления параллельно с работой центрального процессора, не обращая внимание и на переключение задач в защищенном режиме. Синхронизация автоматически обеспечивает ожидание окончания выполнения предыдущей инструкции сопроцессора перед началом выполнения новой (кроме инструкции инициализации, немедленно прерывающей работу сопроцессора) — применения отдельной инструкции WAIT перед каждой командой не требуется (как и в 80287). Сопроцессор может работать в реальном и защищенном режиме и переключать режим разрядности 16/32. Эти режимы влияют только на формат отображения регистров сопроцессора в оперативной памяти, форматы используемых внутренних регистров не изменяются. После аппаратного сброса сопроцессор устанавливается в реальный режим, в котором он программно совместим (обратно) с 8087 и 80287. В защищенный режим сопроцессор переключается по инструкции FSETPM, из которого может вернуться в реальный по инструкции FRSTPM. Перевод в защищенный режим изменяет форматы административных инструкций FLDENV, FSTENV, FRSTOR и FSAVE. Эти инструкции обычно используются только обработчиками исключений, так что на прикладном уровне сопроцессор 32-разрядного процессора (для краткости будем обозначать его как 387+) в любых режимах обратно совместим с 8087 и 80287.

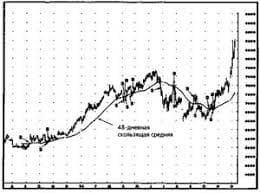

ВОПРОС №12   Конфликты в семейной жизни. Как это изменить? Редкий брак и взаимоотношения существуют без конфликтов и напряженности. Через это проходят все...  Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот...  Что будет с Землей, если ось ее сместится на 6666 км? Что будет с Землей? - задался я вопросом...  Что способствует осуществлению желаний? Стопроцентная, непоколебимая уверенность в своем... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|