|

|

Концепция многоуровневой памятиСтр 1 из 4Следующая ⇒ Организация памяти в ЭВМ ЭВМ, реализованная по классической фон-неймановской архитектуре, включает в себя: • процессор, содержащий арифметико-логическое устройство (АЛУ) и центральное устройство управления (ЦУУ); • память, которая в современных ЭВМ подразделяется на оперативную (ОП или ОЗУ) и сверхоперативную (СОЗУ); • внешние устройства, к которым относят внешнюю память (ВЗУ) и устройства ввода/вывода (УВВ). В этой главе рассмотрим организацию устройств памяти. Принципы взаимодействия других устройств ЭВМ с процессором рассмотрены в разд. 6.3.

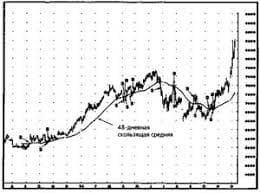

Концепция многоуровневой памяти Известно, что память ЭВМ предназначена для хранения программ и данных, причем эффективность работы ЭВМ во многом определяется характеристиками ее памяти. Во все времена к памяти предъявлялись три основных требования: большой объем, высокое быстродействие и низкая (умеренная) стоимость. Все перечисленные выше требования к памяти являются взаимно-противоречивыми, поэтому пока невозможно реализовать один тип ЗУ, отвечающий всем названным требованиям. В современных ЭВМ организуют комплекс разнотипных ЗУ, взаимодействующих между собой и обеспечивающих приемлемые характеристики памяти ЭВМ для каждого конкретного применения. В основе большинства ЭВМ лежит трехуровневая организация памяти: сверхоперативная (СОЗУ) — оперативная (ОЗУ) — внешняя (ВЗУ). СОЗУ и ОЗУ могут непосредственно взаимодействовать с процессором, ВЗУ взаимодействует только с ОЗУ. СОЗУ обладает максимальным быстродействием (равным процессорному), небольшим объемом (105 — 107 байтов) и располагается, как правило, на кристалле процессорной БИС. Для обращения к СОЗУ не требуются магистральные (машинные) циклы. В СОЗУ размещаются наиболее часто используемые на данном участке программы данные, а иногда — и фрагменты программы. Быстродействие ОЗУ может быть ниже процессорного (не более чем на порядок), а объем составляет 105 — 107 байтов. В ОЗУ располагаются подлежащие выполнению программы и обрабатываемые данные. Связь между процессором и ОЗУ осуществляется по системному или специализированному интерфейсу и требует для своего осуществления машинных циклов. Информация, находящаяся в ВЗУ, не может быть непосредственно использована процессором. Для использования программ и данных, расположенных в ВЗУ, их необходимо предварительно переписать в ОЗУ. Процесс обмена информацией между ВЗУ и ОЗУ осуществляется средствами специального канала или (реже) — непосредственно под управлением процессора. Объем ВЗУ практически неограничен, а быстродействие на 3 — 6 порядков ниже процессорного. Схематически взаимодействие между процессором и уровнями памяти представлено на рис. 5.1.

Следует помнить, что положение ЗУ в иерархии памяти ЭВМ определяется не элементной базой запоминающих ячеек (известны случаи реализации ВЗУ на БИС — "электронный диск" и, наоборот, организация оперативной памяти на электромеханических ЗУ — магнитных барабанах), а возможностью доступа процессора к данным, расположенным в этом ЗУ. При организации памяти современных ЭВМ (МПС) особое внимание уделяется сверхоперативной памяти и принципам обмена информацией между ОЗУ и ВЗУ.

Сверхоперативная память Применение СОЗУ в иерархической памяти ЭВМ может обеспечить повышение производительности ЭВМ за счет снижения среднего времени обращения к памяти Т при условии, что время цикла СОЗУ Тс будет (значительно) меньше времени цикла ОЗУ Т~. Очевидно: где рc — вероятности обращения к СОЗУ. Обозначим так же: рo — вероятности обращения к ОЗУ. Из (5.1) следует, что повышение производительности ЭВМ может осуществляться двумя путями: уменьшением отношения —

увеличением вероятности рc обращения в СОЗУ. Первый путь связан, прежде всего, с технологическими особенностями производства БИС и здесь не рассматривается. Если считать, что информация размещается в СОЗУ и ОЗУ случайным образом, то вероятности рc и рo пропорциональны объемам соответствующих ЗУ. В этом случае рc < рo и наличие в ЭВМ СОЗУ практически не влияет на ее производительность. То же можно было бы сказать и о ситуации, когда отношение Итак, для эффективного применения СОЗУ следует таким образом распределять информацию по уровням памяти ЭВМ, чтобы в СОЗУ всегда располагались наиболее часто используемые в данный момент коды. Принято различать СОЗУ по способу доступа к хранимой в нем информации. Известны два основных класса СОЗУ по этому признаку: • с прямым доступом; • с ассоциативным доступом.

СОЗУ с прямым доступом СОЗУ с прямым доступом (POH — регистры общего назначения) получило широкое распространение в большинстве современных ЭВМ. Фактически РОН — это небольшая регистровая намять, доступ к которой осуществляется специальными командами. Стратегия размещения данных в РОН целиком определяется программистом (компилятором). Обычно в РОН размещают многократно используемые адреса (базы, индексы), счетчики циклов, данные активного фрагмента задачи, что повышает вероятность обращения в ячейки РОН по сравнению с ячейками ОЗУ.

Виртуальная память Выше были рассмотрены способы организации сверхоперативной памяти и ее взаимодействия с оперативной. Не менее, а порой и более важной проблемой является организация взаимодействия в паре ОЗУ — ВЗУ. Известно, что в современных ЭВМ (кроме простейших) реализовано динамическое распределение памяти между несколькими задачами, существующими в ЭВМ в процессе решения. Даже для однозадачных конфигураций проблема динамического распределения памяти не теряет актуальности, т. к. в памяти, помимо задачи пользователя, всегда присутствует операционная система или ее фрагмент. Наличие динамического распределения памяти предполагает, что программа. компилируется в т. н. "логических" адресах, а в процессе работы происходит автоматическое преобразование логических адресов в физические. Наибольшее распространение в ЭВМ получил метод динамического распределения памяти, называемый страничной организацией виртуальной памяти. При использовании этого метода вся память ЭВМ (ОЗУ и ВЗУ) рассматривается как единая виртуальная память. Адрес в этой памяти называется виртуальным или логическим. Вся виртуальная память делится на фрагменты одинакового размера, называемые виртуальными страницами. Размер страницы обычно составляет 0,5 — 4 Кбайт. Виртуальный адрес представляется состоящим из двух частей — номера страницы и номера слова на странице (смещения). Физическая память ЭВМ (ОЗУ и ВЗУ) так же делится на страницы, причем размер физической страницы выбирается равным размеру виртуальной. Таким образом, одна физическая страница может хранить одну виртуальную, причем порядок следования виртуальных страниц в программе совсем не обязательно сохранять на физических страницах. Достаточно лишь установить однозначное соответствие между номерами виртуальных и физических страниц. Соответствие между номерами виртуальных и физических страниц устанавливается с помощью специальной страничной таблицы (СТ), которую поддерживает операционная система. Размер физической страницы равен размеру виртуальной, поэтому преобразования смещений на странице не производятся. Поскольку размер СТ достаточно велик, она хранится целиком в ОЗУ и модифицируется операционной системой всякий раз, когда в распределении памяти происходят изменения. Для увеличения скорости обращения к памяти активная часть СТ обычно хранится в специальной быстродействующей памяти, организованной, как правило, по ассоциативному принципу. При этом в поле признаков АЗУ СТ хранятся виртуальные адреса страниц (иногда вместе с номером программы.— в мультипрограммных системах), а в информационной части — соответствующие им номера физических страниц. Если в результате преобразования виртуального адреса в физический оказывается, что требуемая физическая страница располагается в ВЗУ, то выполнение программы становится невозможным, пока не произойдет "подкачка" требуемой страницы в ОЗУ. Такая ситуация называется страничным сбоем и должна формировать внутреннее прерывание, по которому запускается подпрограмма чтения страницы из ВЗУ в ОЗУ. При этом возникает серьезная проблема поиска той страницы, которую можно удалить из ОЗУ, чтобы на освободившееся место записать требуемую страницу. Серьезность проблемы обусловлена тем, что неудачный выбор удаляемой страницы (в ближайшее время она вновь понадобится) связан со значительной потерей времени на передачу страниц между ОЗУ и ВЗУ.

Алгоритмы замещения Правило, по которому при возникновении страничного сбоя выбирается страница для удаления из ОЗУ, называется алгоритмом замещения. Для данной программы, порождающей некоторый поток обращений к памяти, существует, по крайней мере, одна такая последовательность замещений страниц, которая дает для этой программы минимальное количество страничных сбоев. Теоретически доказано, что минимальное число страничных сбоев будет получено, если в алгоритме замещения использовать информацию о потоке обращений к страницам в будущем (алгоритм Михновского — Шopa) или, по крайней мере, о вероятности обращений к страницам в будущем. Алгоритмы замещения, использующие "информацию о будущем", называются физически нереализуемыми, их обычно применяют для оценки качества эвристических алгоритмов замещения. Эвристические алгоритмы замещения используют информацию о потоке обращений к страницам в прошлом (историю процесса) для экстраполяции характеристик потока обращений в будущем. Как правило, используют три типа информации о прошлом: время пребывания страницы в ОЗУ (или, что то же — очередность поступления страниц), число обращений к страницам за определенный промежуток времени или отрезки времени с момента последнего обращения к страницам. Эффективность эвристического алгоритма можно характеризовать отношением: где N0 — число страничных сбоев при решении данной задачи с применением физически нереализуемого алгоритма; Ne, — то же с применением исследуемого эвристического алгоритма. Эвристический алгоритм можно считать выбранным удачно (для данного класса задач), если коэффициент k близок к 1. Значение N0 может быть получено путем моделирования решения задачи (повторное) с предварительно зафиксированным потоком обращений к страницам. При выборе подходящего алгоритма замещения следует учитывать не только его эффективность k, но и аппаратные затраты и затраты времени на его реализацию. Например, для реализации т. н. НДИ-алгоритма (наиболее давно используемая) каждой странице, находящейся в ОЗУ, ставится в соответствие таймер, который сбрасывается при обращении к странице. При страничном сбое необходимо осуществить поиск максимального элемента массива таймеров страниц. Для некоторых задач выигрыш времени за счет увеличения k при применении НДИ-алгоритма, по сравнению с алгоритмом случайного замещения, может быть сравним с потерей времени на поиск максимальных значений таймеров. Некоторые алгоритмы замещения учитывают одновременно несколько параметров прошлого потока обращений. Алгоритм "Карабкающаяся страница" (KC-алгоритм) поддерживает последовательность номеров страниц, находящихся в ОЗУ. При любом обращении к странице ее номер в последовательности перемещается на одну позицию в направлении начала, меняясь местами с предыдущим в последовательности номером (исключение — обращение к странице, номер которой стоит в начале последовательности). При возникновении страничного сбоя из ОЗУ удаляется страница, номер которой расположен в конце последовательности, а номер вновь поступившей страницы помещается в конец последовательности. КС-алгоритм учитывает как время пребывания страницы в ОЗУ, так и интенсивность обращения к странице, причем не требует значительных аппаратных затрат, а при страничном сбое — времени на поиск. Алгоритм "Рабочий комплект" (PK-алгоритм) более сложен в реализации, но позволяет адаптировать свои параметры под конкретный класс задач. Все страницы ОЗУ, к которым было обращение в течение отрезка времени Т, образуют т. и. рабочий комплект и не подлежат удалению из ОЗУ. Остальные страницы (не вошедшие в рабочий комплект) образуют две очереди кандидатов на замещение, причем в первую очередь попадают страницы, на которые не было записи во время пребывания их в ОЗУ. При страничном сбое удаляется страница из первой очереди (FIFO — первый пришел из рабочего комплекта — первый ушел из ОЗУ), а если первая очередь пуста, то — из второй. Из очереди страница может опять попасть в рабочий комплект, если к ней будет обращение. Для реализации РК-алгоритма каждой странице ставится в соответствие таймер на Т, причем каждое обращение к странице сбрасывает таймер (и переводит страницу в рабочий комплект, если она там отсутствовала), а переполнение таймера выводит страницу из рабочего комплекта. Под- бором величины Т можно оптимизировать РК-алгоритм под конкретный класс задач.

ЧАСТЬ II ГЛАВА 6 Процессорный модуль Процессорный модуль — основная часть любой МПС. Помимо собственно микропроцессора, он включает ряд вспомогательных схем, без которых МПС не может функционировать (тактовый генератор, интерфейсные схемы и др.).

Система команд i8086 Система команд i8086 и, вообще, всего семейства х86 подробно описана в многочисленных справочниках и руководствах, например [11, 12, 13], поэтому далее мы кратко остановимся только на особенностях системы команд |8086, не вдаваясь в излишние подробности. i8086 отличается разнообразием форматов команд и способов адресации. Длина команды может составлять от 1 до 6 байтов, причем в первых двух байтах (иногда — в первом) определяется код операций, количество и длина операндов и способ их адресации. В остальных байтах команды могут размещаться непосредственный операнд, прямой адрес или смещение. Большинство команд i8086 являются двухадресными, причем один адрес определяет регистр процессора, а другой — ячейку памяти или регистр. Операнд в памяти может адресоваться прямо или косвенно посредством содержимого базовых (ВР, ВХ) или индексных (SI, DI) регистров, а также их суммы. Предусмотрены многочисленные варианты относительной адресации, при которых логический адрес образуется как сумма двух или трех слагаемых — одного или двух регистров процессора и 8- или 16-разрядного смещения, размещаемого в команде. Режимы адресации спроектированы с учетом эффективной реализации языков высокого уровня. Например, к простой переменной можно обратиться в режиме прямой адресации, а к элементу массива — в режиме косвенной адресации посредством ВХ, Sl. Режим адресации через ВР предназначен для доступа к данным из сегмента стека, что удобно при реализации рекурсивных процедур и компиляторов языков высокого уровня. Система команд насчитывает 113 базовых команд, объединенных в следующие группы: • команды передачи данных: • между регистрами и памятью (включая стек), обмен содержимым источника и приемника; • ввод, вывод, табличное преобразование; • загрузка исполнительного адреса в РОН, загрузка 4-байтового адресного объекта в регистры-указатели (начальный адрес сегмента и смещение в сегменте); • передача содержимого регистра F флагов в память, в стек и из стека; • арифметические команды: • сложение, вычитание, умножение и деление двоичных чисел со знаком и без знака (произведение и делимое представляются числами двойной длины); • десятичная коррекция сложения и вычитания упакованных двоично-десятичных чисел; • десятичная коррекция сложения, вычитания, умножения и деления распакованных двоично-десятичных чисел; • логические команды и сдвиги: • инверсия, конъюнкция, дизъюнкция, неравнозначность; • TEST — поразрядная конъюнкция операндов с установкой флагов, но без занесения результатов; • сдвиги на 1 или заданное число разрядов (константа сдвига располагается в СЬ); О команды передачи управления: переходы, вызовы, возвраты имеют две разновидности — внутрисегментные ("близкие") и межсегментные ("дальние"). При близких передачах загружается только IP, при дальних— IP и CS. Передачи управления могут быть прямыми (целевой адрес в команде) или косвенными (целевой адрес вычисляется с использованием стандартных режимов адресации). В 16 командах условных переходов проверяются отношения знаковых и без знаковых чисел. Имеются 4 команды управления циклами, которые рассчитаны на размещение числа повторений цикла в регистре СХ; команды обработки цепочек данных манипулируют последовательностями байтов или слов в памяти. Время обработки цепочек этими командами гораздо меньше, чем соответствующей программной реализацией.

Оперативная память Объем адресного пространства МПС с интерфейсом "общая шина" определяется главным образом разрядностью шины адреса и, кроме того, номенклатурой управляющих сигналов интерфейса. Управляющие сигналы могут определять тип объекта, к которому производится обращение (ОЗУ, ВУ, стек, специализированные ПЗУ и др.). В случае, если МП не выдает сигналов, идентифицирующих тип пассивного устройства (или они не используются в МПС) — для селекции берутся только адресные линии. Число адресуемых объектов составляет в этом случае 2, где k — разрядность шины адреса.. Будем называть такое адресное пространство единым. Иногда говорят, что ВУ в едином адресном пространстве "отображены на память", т. е. адреса ВУ занимают адреса ячеек памяти. При использовании информации о типе устройства, к которому идет обращение, одни и те же адреса можно назначать для устройств разных типов, осуществляя селекцию с помощью управляющих сигналов. Так, большинство МП выдают в той или иной форме информацию о типе обращения. В результате в большинстве интерфейсов присутствуют отдельные управляющие линии для обращения к памяти и вводу/выводу, реже — к стеку или специализированному ПЗУ. В результате суммарный объем адресного пространства МПС может превышать величину 2. Например, системная шина МПС на базе микропроцессора i8086 включает 20-разрядную шину адреса и управляющие сигналы, идентифицирующие обращение к памяти (RDM, WRM) и вводу/выводу (RDIO, WRIO). Поэтому в системе доступны 1 Мбайт ячеек памяти (адреса 00000 — FFFFF) + 64 Кбайт адресов ввода + 64 Кбайт адресов вывода (0000 — FFFF). Последняя величина определяется тем, что в командах ввода/вывода процессоров семейства x86 адрес внешнего устройства имеет разрядность 16 битов.

Диспетчер памяти При необходимости расширить объем памяти за пределы адресного пространства можно воспользоваться т. н. диспетчером памяти. В простейшем случае он представляет собой программно-доступный регистр, который должен располагаться в пространстве ввода/вывода. В него заносится номер активного в данный момент банка памяти, причем объем банка может равняться объему адресного пространства МП. Очевидно, в каждый момент времени процессору доступен только один банк. При необходимости перехода в другой банк памяти МП должен предварительно выполнить программную процедуру (часто всего одну команду) перезагрузки содержимого регистра номера банка. К развитию этой идеи можно отнести механизм сегментации памяти в 16- и 32-разрядных МП фирмы Intel.

Организация памяти в ЭВМ ЭВМ, реализованная по классической фон-неймановской архитектуре, включает в себя: • процессор, содержащий арифметико-логическое устройство (АЛУ) и центральное устройство управления (ЦУУ); • память, которая в современных ЭВМ подразделяется на оперативную (ОП или ОЗУ) и сверхоперативную (СОЗУ); • внешние устройства, к которым относят внешнюю память (ВЗУ) и устройства ввода/вывода (УВВ). В этой главе рассмотрим организацию устройств памяти. Принципы взаимодействия других устройств ЭВМ с процессором рассмотрены в разд. 6.3.

Концепция многоуровневой памяти Известно, что память ЭВМ предназначена для хранения программ и данных, причем эффективность работы ЭВМ во многом определяется характеристиками ее памяти. Во все времена к памяти предъявлялись три основных требования: большой объем, высокое быстродействие и низкая (умеренная) стоимость. Все перечисленные выше требования к памяти являются взаимно-противоречивыми, поэтому пока невозможно реализовать один тип ЗУ, отвечающий всем названным требованиям. В современных ЭВМ организуют комплекс разнотипных ЗУ, взаимодействующих между собой и обеспечивающих приемлемые характеристики памяти ЭВМ для каждого конкретного применения. В основе большинства ЭВМ лежит трехуровневая организация памяти: сверхоперативная (СОЗУ) — оперативная (ОЗУ) — внешняя (ВЗУ). СОЗУ и ОЗУ могут непосредственно взаимодействовать с процессором, ВЗУ взаимодействует только с ОЗУ. СОЗУ обладает максимальным быстродействием (равным процессорному), небольшим объемом (105 — 107 байтов) и располагается, как правило, на кристалле процессорной БИС. Для обращения к СОЗУ не требуются магистральные (машинные) циклы. В СОЗУ размещаются наиболее часто используемые на данном участке программы данные, а иногда — и фрагменты программы. Быстродействие ОЗУ может быть ниже процессорного (не более чем на порядок), а объем составляет 105 — 107 байтов. В ОЗУ располагаются подлежащие выполнению программы и обрабатываемые данные. Связь между процессором и ОЗУ осуществляется по системному или специализированному интерфейсу и требует для своего осуществления машинных циклов. Информация, находящаяся в ВЗУ, не может быть непосредственно использована процессором. Для использования программ и данных, расположенных в ВЗУ, их необходимо предварительно переписать в ОЗУ. Процесс обмена информацией между ВЗУ и ОЗУ осуществляется средствами специального канала или (реже) — непосредственно под управлением процессора. Объем ВЗУ практически неограничен, а быстродействие на 3 — 6 порядков ниже процессорного. Схематически взаимодействие между процессором и уровнями памяти представлено на рис. 5.1.

Следует помнить, что положение ЗУ в иерархии памяти ЭВМ определяется не элементной базой запоминающих ячеек (известны случаи реализации ВЗУ на БИС — "электронный диск" и, наоборот, организация оперативной памяти на электромеханических ЗУ — магнитных барабанах), а возможностью доступа процессора к данным, расположенным в этом ЗУ. При организации памяти современных ЭВМ (МПС) особое внимание уделяется сверхоперативной памяти и принципам обмена информацией между ОЗУ и ВЗУ.

Сверхоперативная память Применение СОЗУ в иерархической памяти ЭВМ может обеспечить повышение производительности ЭВМ за счет снижения среднего времени обращения к памяти Т при условии, что время цикла СОЗУ Тс будет (значительно) меньше времени цикла ОЗУ Т~. Очевидно: где рc — вероятности обращения к СОЗУ. Обозначим так же: рo — вероятности обращения к ОЗУ. Из (5.1) следует, что повышение производительности ЭВМ может осуществляться двумя путями: уменьшением отношения —

увеличением вероятности рc обращения в СОЗУ. Первый путь связан, прежде всего, с технологическими особенностями производства БИС и здесь не рассматривается. Если считать, что информация размещается в СОЗУ и ОЗУ случайным образом, то вероятности рc и рo пропорциональны объемам соответствующих ЗУ. В этом случае рc < рo и наличие в ЭВМ СОЗУ практически не влияет на ее производительность. То же можно было бы сказать и о ситуации, когда отношение Итак, для эффективного применения СОЗУ следует таким образом распределять информацию по уровням памяти ЭВМ, чтобы в СОЗУ всегда располагались наиболее часто используемые в данный момент коды. Принято различать СОЗУ по способу доступа к хранимой в нем информации. Известны два основных класса СОЗУ по этому признаку: • с прямым доступом; • с ассоциативным доступом.

СОЗУ с прямым доступом СОЗУ с прямым доступом (POH — регистры общего назначения) получило широкое распространение в большинстве современных ЭВМ. Фактически РОН — это небольшая регистровая намять, доступ к которой осуществляется специальными командами. Стратегия размещения данных в РОН целиком определяется программистом (компилятором). Обычно в РОН размещают многократно используемые адреса (базы, индексы), счетчики циклов, данные активного фрагмента задачи, что повышает вероятность обращения в ячейки РОН по сравнению с ячейками ОЗУ.

Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот...  Конфликты в семейной жизни. Как это изменить? Редкий брак и взаимоотношения существуют без конфликтов и напряженности. Через это проходят все...  Что способствует осуществлению желаний? Стопроцентная, непоколебимая уверенность в своем...  Что делать, если нет взаимности? А теперь спустимся с небес на землю. Приземлились? Продолжаем разговор... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|