|

|

ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫГлава 1. Основные параметры логических схем В импульсных устройствах вычислительной техники и цифровой автоматики широко применяются интегральные микросхемы, позволяющие автоматизировать выполнение определённых операций, последовательность и порядок которых задается необходимыми функциями. В качестве простейших элементов таких устройств используются интегральные логические элементы /ИЛЭ/, которые работают по принципу ключа, но при нескольких входных сигналах. Функциональная схема ИЛЭ включает в себя, как правило, три части: o o o формирующая, обычно сочетается со второй и обеспечивает формирование выходного сигнала заданного уровня. Все логические интегральные микросхемы можно разделить на три группы: · ИЛЭ с передачей тока или напряжения на вход нагрузочного элемента (резистивно-ёмкостная транзисторная логика РЕТЛ, транзисторная логика с непосредственной связью на биполярных или МДП-транзисторах, логика с двойной инжекцией И2Л (инжекционным питанием, интегральная инжекционная); · ИЛЭ с логикой на входе, – конъюнкция или дизъюнкция, с последующей передачей тока на формирующий элемент: (диодно-транзисторная логика ДТЛ, транзисторно-транзисторная логика ТТЛ, транзисторная логика с переменным порогом срабатывания ППТЛ); · ИЛЭ с эмиттерной связью и токовым переключением (эмиттерно-связанная логика ЭСЛ). Как и в простейших ключах на транзисторах все параметры ИЛЭ делятся на статические и динамические. К группе статических параметров относятся: входные токи и напряжения высокого и низкого уровней: Ø пороговые напряжения низкого и высокого уровня Ø помехоустойчивость ИЛЭ, определяемая в режиме низкого или высокого уровней выходного сигнала, связана с изменением входного напряжения по отношению к пороговому так, чтобы при этом уровень выходного сигнала Ø коэффициент разветвления по выходу КРАЗ, определяет нагрузочную способность ИЛЭ. Он показывает, какое число аналогичных ИЛЭ может быть подключено к выходу заданного и при этом его работоспособность должна отвечать предъявляемым техническим требованиям. Ø коэффициент объединения по входу КОБ, показывает число аналогичных ИЛЭ, которое можно подключить вместе с заданным, так чтобы его работоспособность отвечала предъявляемым техническим требованиям. Ø потребляемая мощность в режиме логического нуля Большинство статических параметров можно оценить с помощью передаточной характеристики ИЛЭ по напряжению. Передаточная характеристика, это графическая зависимость одноименных параметров напряжения или тока. Наибольшее распространение получила передаточная характеристика ИЛЭ по напряжению, то есть зависимость выходного напряжения при изменении входного (рис. 2.3).

К группе динамических параметров относятся, в основном, времена, характеризующие быстродействие ИЛЭ: Ø время задержки при переходе ИЛЭ по выходному состоянию из низкого уровня напряжения в высокий Ø времена фронта и среза, определяемые по размаху выходного напряжения при переключении ИЛЭ – Ø работа переключения, которая находится как произведение потребляемой мощности и времени задержки. Обычно это Все времена переходного процесса находятся из переходных характеристик ИЛЭ, которые представлены на рис. 2.4.

Нечетное число ИЛЭ объединяются в кольцевую схему, в которой при достаточно большом числе ИЛЭ происходит самовозбуждение с периодом колебаний Т (рис. 2.5). На одном из выходов схемы имеет место максимальная ам Идеальный интегральный логический элемент должен обладать максимальным быстродействием, высокой помехоустойчивостью, широкими функциональными возможностями, малой мощность рассеивания, не создавать бросков тока в источнике питания при переключении. 1.1. Транзисторно-транзисторная логика Данная логика является наиболее распространённой логической схемой, для которой характерно наличие многоэмиттерного транзистора МЭТ. Наибольшее распространение получила схема со сложным инвертором (рис. 2.6).

На рис. 2.7 показана передаточная характеристика ТТЛ-элемента со сложным инвертором. Её положение зависит от состояния элементов схемы. При малом входном сигнале При увеличении входного напряжения (участок II) подзапирается транзистор VT3, увеличивается потенциал на его коллекторе, то есть изменяется напряжение на базе транзистора VT1. За счёт увеличения этого напряжения увеличивается ток базы транзистора VT1 и соответственно его коллекторный ток, что приводит к увеличению падения напряжения на резисторе R1. Это падение напряжения передаётся на выход схемы. Таким образом, на этом участке имеет место При достижении входным сигналом величины 1,4 В открывается транзистор VT3 (начало III-го участка). При этом режиме закрывается МЭТ, транзисторы VT1 и VT3 работают в активном режиме. Полное запирание МЭТ и насыщение транзистора VT1 имеет место, когда входной сигнал достигнет уровня 1,5 В. В этом случае транзистор VT3 становится насыщенным, МЭТ работает в инверсном режиме (IV участок). Обратное переключение на выходе (от уровня логического «0» до уровня логической «1»), осуществляется в обратной последовательности с соответствующим изменением режимов элементов схемы. Коэффициент разветвления находится исходя из одного из следующих условий: · насыщения транзистора VT3 или VT1; · обеспечения допустимого уровня выходного сигнала · помехоустойчивости в режиме логического «нуля» или логической «единицы»; · быстродействия схемы.

На схеме рис. 2.8 слева расположен МЭТ1 основного ТТЛ-элемента, справа – МЭТ2 нагрузочного ТТЛ-элемента. Условие насыщения транзистора VT3 имеет вид:

Ток в цепи нагрузки ТТЛ-элемента проходит черезМЭТ2 и равен:

Соответственно: где - Ток базы МЭТ2 можно выразить как:

Ток базы насыщенного транзистораVT3 состоит из алгебраической суммы трёх токов:

Каждый из этих токов можно выразить следующим образом:

Подставляя в формулу условия насыщения транзистора VT3 зависимости для всех коэффициентов можно получить результирующее выражение для коэффициента разветвления схемы. Пренебрегая остаточными напряжениями насыщенных транзисторов и с учётом упрощений это выражение имеет вид:

В реальном случае коэффициент разветвления ТТЛ-эле-мента, полученный из условия насыщения транзистораVT3, имеет величину Коэффициент разветвления ТТЛ-элемента, полученный из различных условий имеют примерные значения: - из условия обеспечения уровня логического нуля – 23; - из условия обеспечения помехоустойчивости в режиме логического нуля – 18; - из условия быстродействия – 10; Обычно эта величина принимается равной Помимо схемы с классическим сложным инвертором существуют и другие разновидности схем ТТЛ-элементов, нашедших широкое применение (рис. 2.9). На этом рисунке пороговое напряжение находится как:

и составляет величину порядка 2,1 В. В серию интегральных микросхем помимо основных элементов входят и вспомогательные, позволяющие увеличить функциональные возможности элементов. На рис. 2.10 показана схема расширителя по ИЛИ, а на рис. 2.11 показан пример рас расширения функциональных возможностей схемы ТТЛ-элемента, выполняющего функцию 3И-2ИЛИ-НЕ (рис. 2.11а)) и его функциональное обозначение (рис. 2.11б)). Следует отметить, что подключение к основному элементу расширителя приводит к увеличению потребляемой мощности, а также снижается нагрузочная способность и быстродействие ТТЛ-элемента. Другой разновидностью ТТЛ-элемента является схема с открытым коллектором (рис. 2.12), часто используемая в цепях индикации состояния схемы.

К выходу схемы U4 (рис.2.12) может быть подключен световой индикатор со своим источником питания. Это имеет место в том случае, когда питание светового индикатора не равно напряжению питания интегральной микросхемы.

При наличии сигнала на запрещающем входе UZ закрыты транзисторы VT2 и VT3, и на выходе U4 имеет место нулевой потенциал. Таким образом, на выходе интегрального логического

Достоинствами ТТЛ-элементов являются: o высокий уровень технологии с большим процентом выхода годных схем; o стабильность электрических параметров; o высокая помехоустойчивость, особенно в режиме логического нуля; o наиболее полно представлено разнообразие элементной базы выпускаемых схем. К недостаткам ТТЛ-элементов относятся: o ограниченное быстродействие (повышение быстродействия производится при использовании транзисторов Шоттки), o трудности согласования с другими элементами, выполненными не по ТТЛ-технологии, o броски токов в выходной цепи при переключении. 1.2. Эмиттерно-связанная логика Основу схемы эмиттерно-связанной логики – ЭСЛ составляет дифференциальный каскад, работающий в режиме переключения токов (рис. 2.14).

Максимальное значение коллекторного потенциала равно Эмиттерно-связанная логика является в настоящее время наиболее быстродействующей логикой, так как наибольшую часть времени переключения транзисторы схемы работают в линейном режиме, и очень малое время находятся в квазистатическом состоянии.

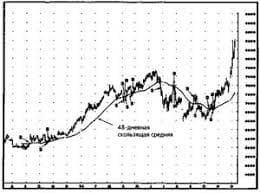

В верхней части характеристик показаны изменения потенциалов на коллекторах входного касскада, в нижней части напряжения на выходах схемы при изменениях входного сигнала по сравнению с опорным базовым напряжением ЕБ. На рисунке приведены цифры напряжений, характерные для базового элемента 500-ой интегральной серии при ЕП = 5В. ЭСЛ-элемент по сравнению с ТТЛ-элементом, обладает повышенной нагрузочной способностью; это обеспечивается подключением на выходах эмиттерных повторителей (рис. 2.16), которые и обуславливают наличие смещения ЕСМ =Ео1 / Ео2. На этом рисунке показана схема ЭСЛ-элемента, выполняющего логические функции 4ИЛИ (для выхода U6), и 4ИЛИ-НЕ (для выхода U5). Базовый элемент опорного напряжения собран на транзисторе VT6 и с него подается на вход транзистора VT5 постоянное напряжение ЕБ= 1,175В при ЕП =5 В. В практической Выходные транзисторы VT7 и VT8, выполняют функции усилителей мощности, позволяют улучшить нагрузочную способность схемы и являются буферными каскадами для разделения нагрузку от переключателя токов (основной части схемы). Схема ЭСЛ–элемента обладает большими функциональными возможностями по сравнению с элементами ТТЛ-логики, так как позволяет получать на выходе как инвертированный, так и неинвертированный входной сигнал, снимаемый с разных выходов. При переключениях схемы транзисторы переключательного каскада работают в линейном режиме без насыщения и практически по схеме с ОБ, процесс переключения которой характеризуется параметром транзистора τα. Это обуславливает высокое быстродействие ЭСЛ-элемента по сравнению с другими логическими элементами. Так как схема ЭСЛ-элемента не имеет больших перепадов выходного тока (напряжения), которые характерны для ТТЛ- или ДТЛ-элемента, поэтому величины сопротивлений RК невелики и перезарядка паразитных ёмкостей в коллекторных цепях транзисторов протекает быстрее. Существенным недостатком схемы отечественного ЭСЛ-элемента является напряжение отрицательной полярности. Тем самым затруднена связь ЭСЛ- элементов с элементной базой других интегральных серий. Часть вторая   Что делать, если нет взаимности? А теперь спустимся с небес на землю. Приземлились? Продолжаем разговор...  ЧТО ПРОИСХОДИТ, КОГДА МЫ ССОРИМСЯ Не понимая различий, существующих между мужчинами и женщинами, очень легко довести дело до ссоры...  Живите по правилу: МАЛО ЛИ ЧТО НА СВЕТЕ СУЩЕСТВУЕТ? Я неслучайно подчеркиваю, что место в голове ограничено, а информации вокруг много, и что ваше право...  Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|