|

|

ИНТЕГРАЛЬНЫЕ РЕГИСТРЫ В ПРОГРАММНОЙ СРЕДЕ EWB

На этом рисунке выводы 1D, 2D, 3D, 4D – входы регистра с логическими элементами разрешения записи путём подачи логического 0 на входы M, N. Выходы Q1, Q2, Q3, Q4 выполнены с третьим высокоомным Z – состоянием (при сигнале 1 на выводах G1’, G2’). Запись информации в регистр производится по положительному перепаду тактового импульса на входе CLK, если на входы M, N подано напряжение низкого уровня. Сигнал очистки регистра CLR имеет высокий активный уровень. Дальнейшее изучение работы регистра проводится по нижеприведенной таблице состояний, табл. 3.10. Высокоомное состояние позволяет организовать работу нескольких регистров памяти на общую шину – электрически выходы всех регистров объединены, но в каждый момент времени на шину работает только один из них. Выбор работающего регистра определяют сигналы на входах G1’и G2’. При этом данные из других регистров в общую шину не проходят, выходы регистра не влияют на работу других аналогичных выходов, присоединенных к проводникам общей шины. Таблица 3.10

На рис. 3.38 в качестве примера приведена схема двух интегральных регистров 74173, работающих на общую шину. На верхний регистр подаётся изменяющаяся двоичная информация с генератора слов, а на нижний регистр постоянное двоичное слово 1000. В соответствии с управляющими сигналами на входах M, N, G1’, G2’ регистров на общую шину передаётся информация то с верхнего регистра, то с нижнего. Семисегментные и светодиодные индикаторы позволяют наглядно изучить работу устройства. 2. В окне программной среды EWB загрузить файл «Reg3» для изучения второго класса регистров - регистров сдвига на примере библиотечного регистра 74195 (К155ИР12). Это быстродействующий регистр для выполнения операций сдвига, счёта, накопления и взаимного параллельно-последовательного преобразования двоичных слов. На рис. 3.39 показано обозначение регистров сдвига ИМС 74195 на принципиальных и функциональных электрических схемах.

Таблица 3.11

В этой таблице QA0, QB0, QC0, QD0 и QАn, QBn, QCn, QDn – значения выходных сигналов регистра до и сразу после положительного перепада сигнала CLK соответственно. Включение ИМС 74195 в режиме приёма данных исследуется в схеме, приведенной на рис. 3.40. В этой схеме генератор слов задаёт последовательность двоичных слов, каждое из которых записывается в регистр по положительному перепаду тактового сигнала и появляется на выходе регистра.

Работа сдвигового регистра хорошо иллюстрируется временными диаграммами, полученными с помощью логического анализатора и приведёнными ниже (см. рис. 3.42). Между двумя вертикальными визирами логического анализатора сверху вниз регистрируются следующие сигналы: тактовые сигналы, которые определяют значение времени задержки при сдвиге информации; входная информация произвольного вида на объединённых входах регистра сдвига (J и K); выходные сигналы регистра (QA, QB, QC, QD), которые представляют собой сигналы с прямых выходов каждого из четырёх триггеров в составе регистра. Видно, что временной сдвиг входной информации происходит по положительному перепаду

4. В качестве самостоятельного задания студентам предлагается разработать схему четырехфазного распределителя тактовых импульсов на основе сдвигового регистра 74195 и простейших логических элементов 2И-НЕ и 4ИЛИ-НЕ. Использовать индикаторные элементы, подключаемые к выходам разработанной схемы. Наблюдать визуально работу распределителя при частоте входных сигналов (1 - 2)Гц. Выделить в разработанном устройстве узлы, выходные сигналы которых представляют собой распределенные единичные уровни напряжения.

Рис. 3.42. Работа сдвигового Регистра

ИНТЕГРАЛЬНЫЕ СЧЁТЧИКИ В ПРОГРАММНОЙ СРЕДЕ EWB В программной среде EWB широко представлены ИМС двоичных и двоично-десятичных, суммирующих и реверсивных, с последовательным и параллельным переносом, с предва-рительной загрузкой и без загрузки счётчиков. 1. В окне программной среды EWB загрузить файл «Counter1» для изучения двоичного суммирующего четырёхразрядного счётчика с предварительной загрузкой 74163 (К155ИЕ18), представленного на рис. 3.43.

Таблица 3.12

Из приведённой таблицы видно, что сигнал CLR имеет наивысший приоритет; загрузка предварительного кода осуществляется по положительному перепаду тактового сигнала CLK при нулевых значениях сигналов ENT и ENP; счёт (Count), то есть добавление 1 к содержимому счётчика, осуществляется также по положительному перепаду CLK при единичных значениях переменных ENT и ENP. Счётчик содержит внутреннюю логику ускоренного переноса, и все триггеры получают перепад тактового сигнала одновременно. Изменения выходных состояний триггеров совпадают по времени, поэтому в выходных импульсных последовательностях нет "пиковых" помех. Схема включения ИМС 74163 приведена на рис. 3.44, где для индикации состояний счётчика использован логический анализатор, а источником входных управляющих и информационных сигналов служит генератор слов. При этом по длительности указанные сигналы распределены следующим образом: самый длительный сигнал CLR, далее по порядку ENT, ENP и CLK. Из приведённой схемы видно, что предварительно загружаемый код 1001, поэтому счёт будет осуществляться с кода 1001 до кода 1111. Дальнейшая работа счётчика зависит от совокупно-

сти управляющих сигналов. Работа схемы иллюстрируется с помощью логического анализатора, рис. 3.45. Между вертикальными визирами сверху вниз регистрируются сигналы CLR, LOAD’, ENP, ENT, CLK, QA, QB, QC, QD, RCO. Видно, что по каждому положительному перепаду сигнала CLK к содержимому счётчика добавляется 1, при этом счёт начинается с кода 1001 и заканчивается кодом 1111, возникает сигнал переноса RCO и счётчик обнуляется.

Дополнительный сигнал D/U’ позволяет изменять направление счёта в соответствии с таблицей состояний, приведённой ниже, табл. 3.13. Таблица 3.13

Как видно из таблицы изменение содержания счётчика происходит по отрицательному перепаду сигнала CLK. На рис. 3.47 приведена схема включения счётчика 74169, позволяющая изучить его работу в режиме вычитания без предварительной загрузки. Ниже приводятся временные диаграммы, полученные с помощью логического анализатора, рис. 3.48. Между вертикальными визирами сверху вниз приведены следующие сигналы LOAD, CLK, QA, QB, QC, QD, RCO. Видно, что идёт вычитание 1 из содержимого счётчика по каждому отрицательному перепаду сигнала CLK. Содержимое счётчика циклически изменяется от кода 1111 до кода 0000. 3. В программной среды EWB загрузить файл «Counter3» для изучения работы ИМС 74160 (К155ИЕ9). Это суммирующий счётчик, работающий с коэффициентом счёта 10 в двоично–десятичном коде (в двочном – по коду счёта, десятичным - по числу состояний). Счётчик показан на рис. 3.49. Ниже приведена таблица 3.14 его состояний, из которой следует, что сигнал переноса в этом счётчике возникает при достижении кода 1001. При выходных сигналах высокого уровня счётчик К155ИЕ9 потребляет ток питания 94мА, если все выходные сигналы имеют низкий уровень, то – 100мА. Максимальная частота счета счётчика 25 МГц. Время распространения сигнала от входа CLK до выхода RCO составляет 35 нс, а время сброса (от входа R до выходов Q) – 38 нс. Таблица 3.14

4. В качестве самостоятельного задания студентам можно предложить разработать схему цифровых часов. Часы должны содержать три пары индикаторов для отображения часов, минут и секунд и два одиночных индикатора-разделителя. В качестве индикаторов использовать библиотечные 7-сегментные цифровые индикаторы со встроенным дешифратором, которые можно подключать непосредственно к выходам двоично-десятичных счётчиков. Индикаторы управляются пересчётными схемами на триггерах с коэффициентами пересчёта 24 и 60. В качестве задающего генератора можно использовать функциональный генератор прямоугольных импульсов с частотой следования 1 Гц, скважностью 50%, амплитудой 2 В и сдвигом уровня 2 В. Пересчётная схема на 60 может, например, состоять из двоично-десятичного счётчика и асинхронного трёхразрядного счётчика с коэффициентом пересчёта 6. Пересчётная схема на 24, в свою очередь, может быть построена на основе асинхронного пятиразрядного счётчика с устранением восьми лишних состояний.

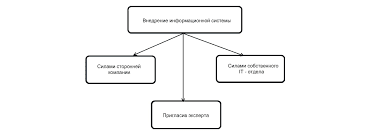

Что делает отдел по эксплуатации и сопровождению ИС? Отвечает за сохранность данных (расписания копирования, копирование и пр.)...  ЧТО И КАК ПИСАЛИ О МОДЕ В ЖУРНАЛАХ НАЧАЛА XX ВЕКА Первый номер журнала «Аполлон» за 1909 г. начинался, по сути, с программного заявления редакции журнала...  Живите по правилу: МАЛО ЛИ ЧТО НА СВЕТЕ СУЩЕСТВУЕТ? Я неслучайно подчеркиваю, что место в голове ограничено, а информации вокруг много, и что ваше право...  ЧТО ТАКОЕ УВЕРЕННОЕ ПОВЕДЕНИЕ В МЕЖЛИЧНОСТНЫХ ОТНОШЕНИЯХ? Исторически существует три основных модели различий, существующих между... Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

|